### Efficient Transmitters for Wireless Communications in Nanoscale CMOS Technology

Debopriyo Chowdhury

### Electrical Engineering and Computer Sciences University of California at Berkeley

Technical Report No. UCB/EECS-2010-168 http://www.eecs.berkeley.edu/Pubs/TechRpts/2010/EECS-2010-168.html

December 17, 2010

Copyright © 2010, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### Efficient Transmitters for Wireless Communications in Nanoscale CMOS Technology

by

Debopriyo Chowdhury

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

$\mathrm{in}$

Engineering - Electrical Engineering and Computer Sciences

in the

Graduate Division

of the

University of California, Berkeley

Committee in charge:

Professor Ali M. Niknejad, Chair Professor Elad Alon Professor Paul Wright

Fall 2010

# Efficient Transmitters for Wireless Communications in Nanoscale CMOS Technology

Copyright 2010 by Debopriyo Chowdhury

#### Abstract

by

Debopriyo Chowdhury

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Ali M. Niknejad, Chair

The last decade has witnessed a tremendous growth in wireless communications. Todays consumers demand wireless systems that are low-cost, power efficient, reliable and have a small form-factor. This quest for ubiquitous wireless connectivity and the trend toward highly integrated solutions have opened up a new wave of challenges and opportunities for RF (radio-frequency) integrated circuit design. Since it often dictates both battery life and form factor, the transmitter and in particular the power amplifier (PA) is often the most challenging block in this integrated radio design. The grand vision for wireless transmitters is to merge as many components as possible, if not all, into a single die in an inexpensive technology. There is therefore growing interest in utilizing CMOS technologies for power amplifiers (PAs). However, the low-supply voltage of nanoscale CMOS technology, the loss of on-chip passives and the conductive silicon substrate make a fully-integrated PA design challenging. This thesis focuses on the design of fully-integrated PAs for modern wireless communication systems at RF (2.4GHz) as well as 60GHz frequencies. Transformer based matching networks have been studied for PA design and new modeling methods proposed in this work. It has been shown that there is tremendous area benefit of using transformers at 60GHz, while still preserving high performance. A prototype of a transformer-coupled PA has been designed at 60GHz in 90nm CMOS technology. The transformer design and modeling proposed at 60GHz is equally valid at RF frequencies. However, the high output power and high linearity requirements at RF frequencies create further challenges. Conventional power amplifier architectures are showing limitations in terms of achievable efficiency and area reduction. In particular, such architectures are not benefiting much from technology scaling since the area is dominated by passive elements. In this thesis, we investigate a mixedsignal power amplifier architecture. By merging our work on transformer-coupled PAs with a digital signal processing framework, a truly scalable, efficient transmitter architecture can be created. Such a prototype has been designed and tested in 65nm CMOS technology.

To The All-Mighty Goddess Ma Kali

## Contents

| List of Tables |      |                                                                         | iv        |

|----------------|------|-------------------------------------------------------------------------|-----------|

|                |      |                                                                         | ix        |

| 1              | Intr | oduction                                                                | 1         |

| <b>2</b>       | Pas  | sive Matching Networks for Power Amplifier Design                       | 8         |

|                | 2.1  | LC Matching Networks                                                    | 8         |

|                | 2.2  | Transformer-Based Matching Networks                                     | 11        |

|                | 2.3  | Transformers at 60GHz                                                   | 15        |

|                |      | 2.3.1 Lumped Modeling of mm-wave Transformers                           | 20        |

|                |      | 2.3.2 Distributed Modeling of Transformers                              | 23        |

|                | 2.4  | Transformers and Transformer-Based Power Combiners at RF Frequencies .  | 27        |

|                |      | 2.4.1 A 2.4GHz Parallel-Primary Transformer with Interwound Secondary . | 27        |

|                |      | 2.4.2 Transformer Based Power Combiner Design                           | 30        |

|                | 2.5  | Summary                                                                 | 35        |

| 3              | 60G  | Hz Transformer-Coupled Power Amplifiers                                 | <b>37</b> |

|                | 3.1  | 60GHz PA Specifications                                                 | 37        |

|                | 3.2  | Power Transistors at mm-wave Frequencies                                | 38        |

|                | 3.3  | Design Methodology for PA with Transformers                             | 41        |

|                | 3.4  | PA Stability Considerations                                             | 44        |

|                | 3.5  | Two-stage PA Simulation and Measurement Results                         | 46        |

|                |      | 3.5.1 Class AB Biasing at 60 GHz                                        | 51        |

|                | 3.6  | Three Stage 60GHz PA Design and Integrated Transmitter                  | 52        |

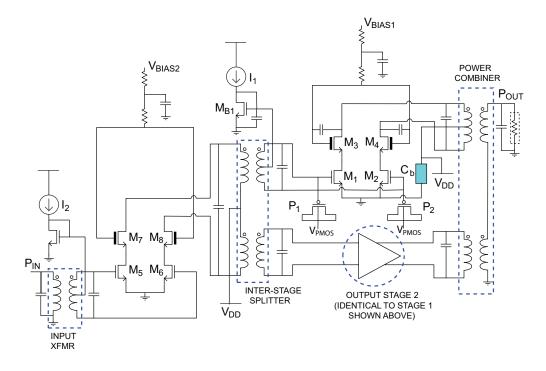

|                |      | 3.6.1 Three-stage PA Measurement Results                                | 54        |

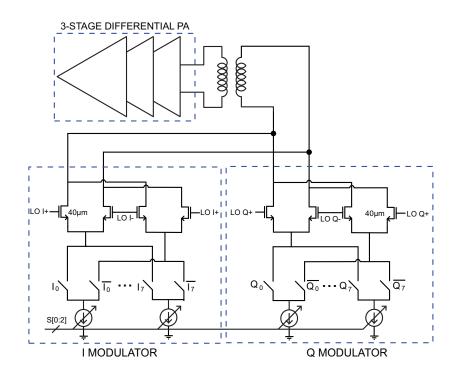

|                |      | 3.6.2 PA-Modulator Interface Design                                     | 54        |

|                | 3.7  | Summary                                                                 | 58        |

| 4              | Line | ear RF Power Amplifiers Supporting Multi-Level Modulation               | <b>59</b> |

|                | 4.1  | Two-Stage High-Power Highly-Linear PA Design                            | 60        |

iii

61

66

|              |                        | 4.1.3 Bypass Network and Common-Mode Stability | 67  |

|--------------|------------------------|------------------------------------------------|-----|

|              | 4.2                    | Measurement Results                            | 68  |

|              | 4.3                    | Transformer Power Back-Off                     | 72  |

|              | 4.4                    | Summary                                        | 76  |

| <b>5</b>     | A 2                    | .4GHz Mixed-Signal Polar Power Amplifier       | 77  |

|              | 5.1                    | Inverse Class-D PA as Unit Cell                | 80  |

|              |                        | 5.1.1 Practical Design Considerations          | 82  |

|              |                        | 5.1.2 Matching Network for Class- $D^{-1}$ PA  | 88  |

|              | 5.2                    | PA as an RF-DAC                                | 92  |

|              |                        | 5.2.1 Targeted Standard: 802.11g               | 92  |

|              |                        | 5.2.2 Amplitude and Phase Resolution           | 94  |

|              |                        | 5.2.3 Power Back-Off and Efficiency            | 95  |

|              |                        | 5.2.4 Amplitude and Phase Linearity            | 100 |

|              |                        | 5.2.5 Clocking Rates and Digital Filter        | 102 |

|              |                        | 5.2.6 Implementation and Layout of the RF-DAC  | 103 |

|              | 5.3                    | Low-power Digital Filter Design                | 106 |

|              | 5.4                    | Measurement Results                            | 110 |

|              |                        | 5.4.1 Board Layout and Measurement Setup       | 110 |

|              |                        | 5.4.2 Measured Results                         | 112 |

|              | 5.5                    | Summary                                        | 120 |

| 6            | Con                    | nclusion                                       | 121 |

|              | 6.1                    | Thesis Summary                                 | 121 |

|              | 6.2                    | Future Directions                              | 123 |

| Bibliography |                        |                                                |     |

| A            | $\mathbf{P}\mathbf{A}$ | Stability Analysis                             | 130 |

4.1.1

4.1.2

# List of Figures

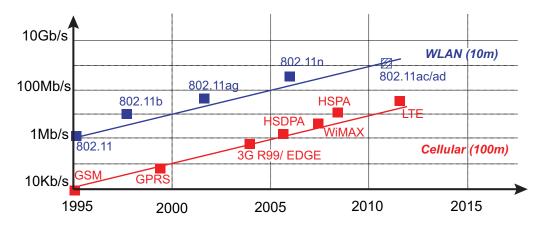

| 1.1  | Growth of high data rate wireless communications [1]                                       | 2  |

|------|--------------------------------------------------------------------------------------------|----|

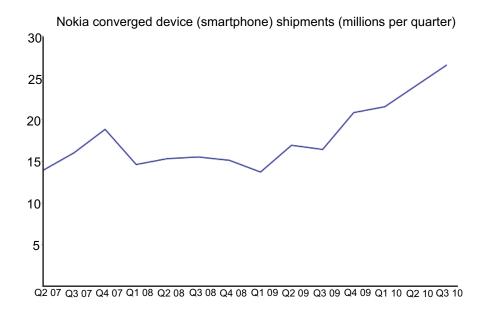

| 1.2  | Growth in the sale of Nokia converged devices (smartphones) [2]                            | 2  |

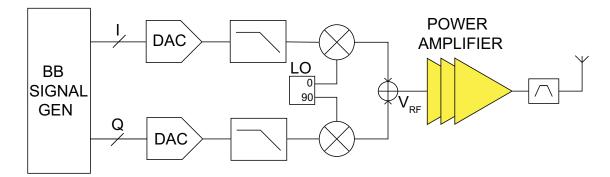

| 1.3  | Block diagram of a wireless transmitter.                                                   | 3  |

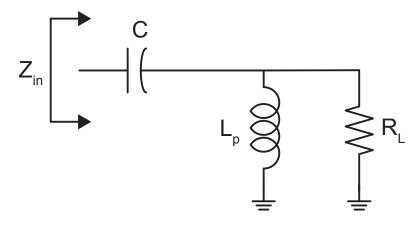

| 2.1  | A single stage "L-match" with a series capacitor and a parallel inductor                   | 9  |

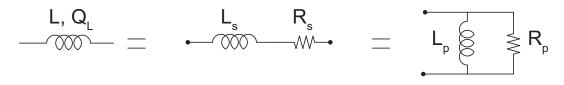

| 2.2  | Equivalent models of an inductor with quality factor $Q_L$                                 | 9  |

| 2.3  | Single stage L-match network with inductor loss                                            | 10 |

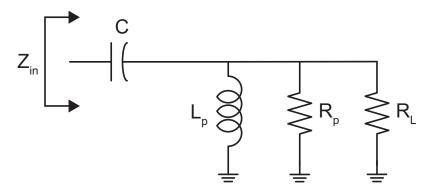

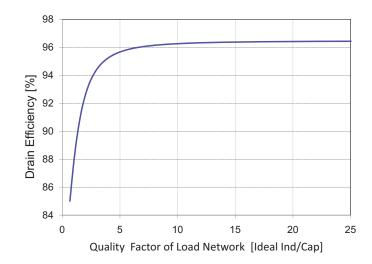

| 2.4  | Efficiency of an LC matching network for different inductor quality factors                | 11 |

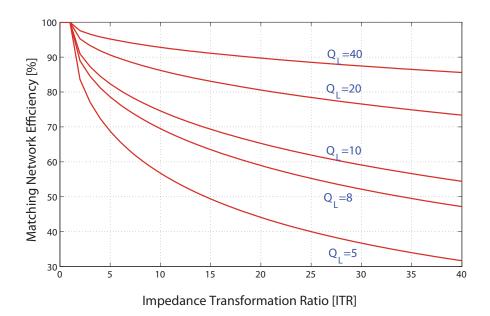

| 2.5  | Ideal transformer model                                                                    | 12 |

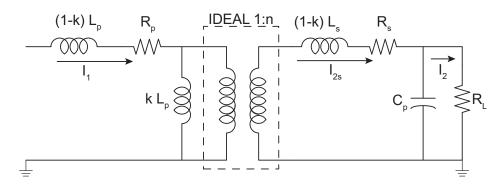

| 2.6  | Simplified model of a 1:n transformer                                                      | 12 |

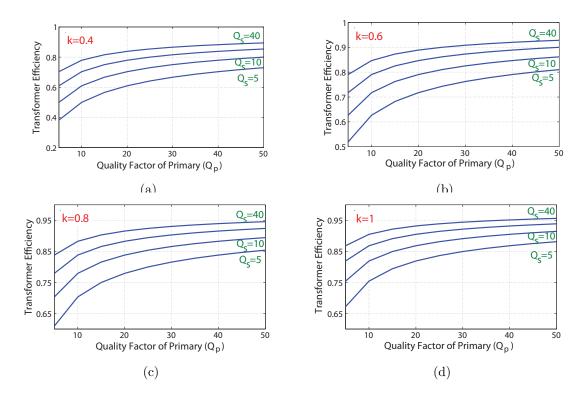

| 2.7  | Transformer efficiency for different primary and secondary winding quality                 |    |

|      | factors for a) $k = 0.4$ b) $k = 0.6$ c) $k = 0.8$ and d) $k = 1.0.$                       | 14 |

| 2.8  | Equivalent circuit of a 1:1 transformer                                                    | 16 |

| 2.9  | Variation of $L_{eff}$ and SRF with diameter of inductor                                   | 16 |

| 2.10 | Layout of a 1:1 transformer using coupled inductors in a vertical configuration.           | 16 |

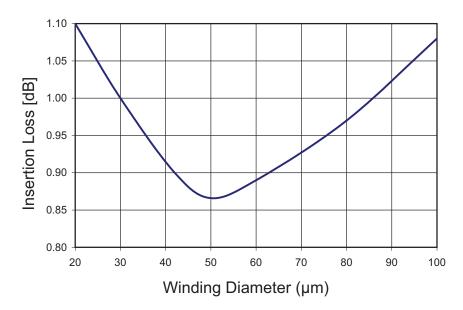

| 2.11 | Variation of insertion loss of transformer at 60GHz as a function of winding               |    |

|      | diameter                                                                                   | 17 |

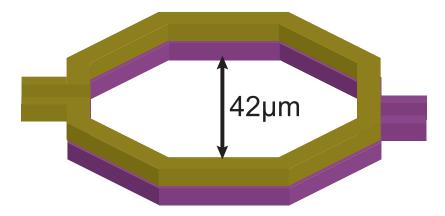

| 2.12 | Die photo of a transformer with a diameter of $42\mu m$ and width of $8\mu m$              | 18 |

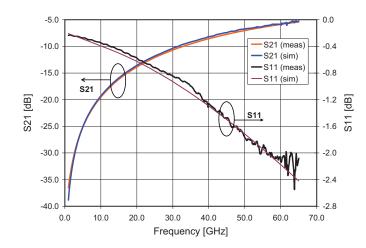

| 2.13 | Simulated and measured s-parameters for a vertical transformer                             | 19 |

| 2.14 | Measured insertion loss for a 1:1 vertical transformer                                     | 19 |

| 2.15 | Dependence of transformer performance on substrate parameters                              | 20 |

| 2.16 | Input admittance of a transformer for a) different winding diameters at 60GHz              |    |

|      | b) a winding diameter of $42\mu m$ at different frequencies                                | 21 |

| 2.17 | Symmetric $2\pi$ model of transformer                                                      | 21 |

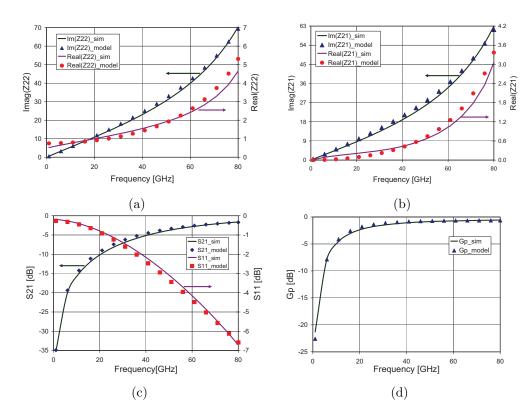

| 2.18 | Comparison between simulated and model results a) $Z_{22}$ b) $Z_{21}$ c) $S_{11}/S_{21}$  |    |

|      | and d) $G_p$                                                                               | 23 |

| 2.19 | Distributed modeling of a transformer as coupled transmission-lines                        | 24 |

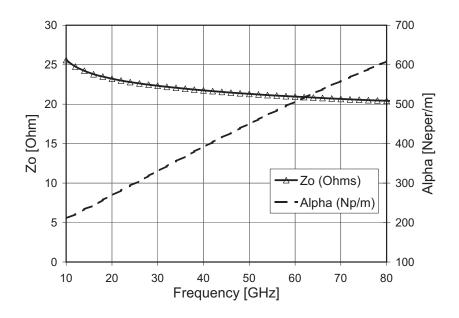

| 2.20 | Characteristic impedance $(Z_0)$ and loss factor $(\alpha)$ of a $30\mu$ m diameter trans- |    |

|      | former, excited as a transmission line                                                     | 25 |

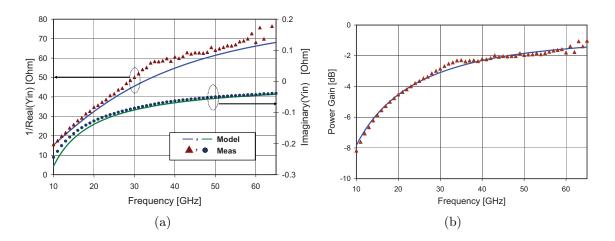

| 2.21 | 1 / 1                                                                                      |    |

|      | admittance $(Y_{in})$ and b) power gain $(G_p)$ .                                          | 26 |

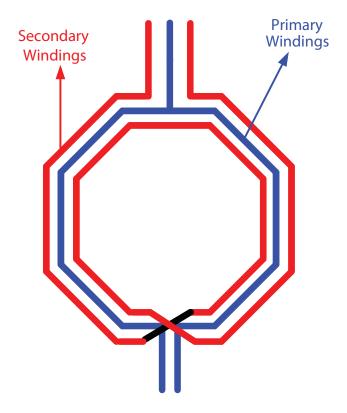

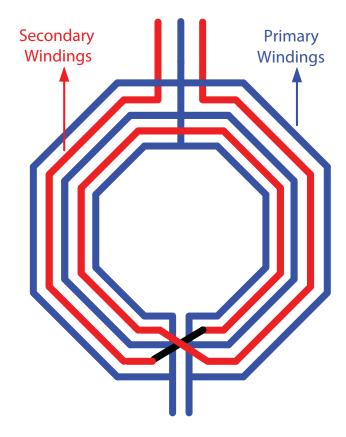

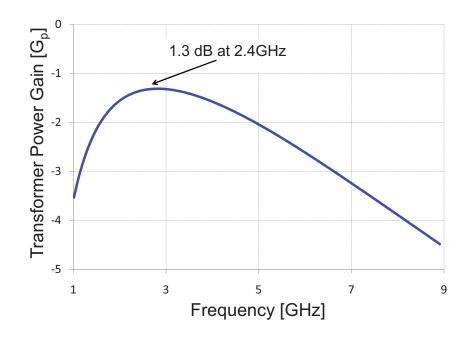

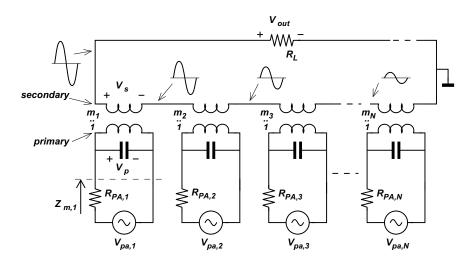

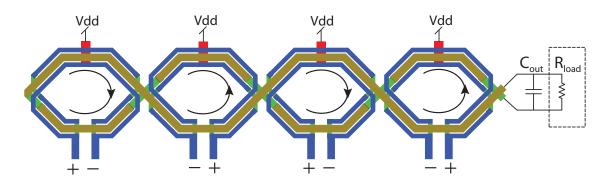

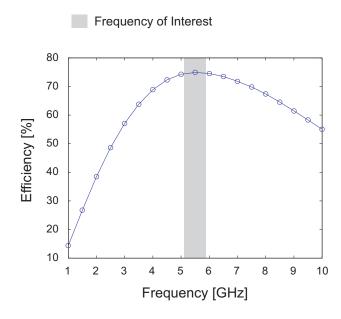

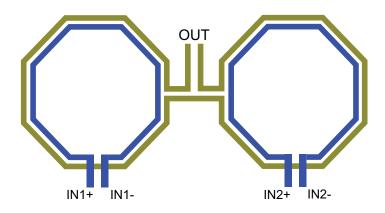

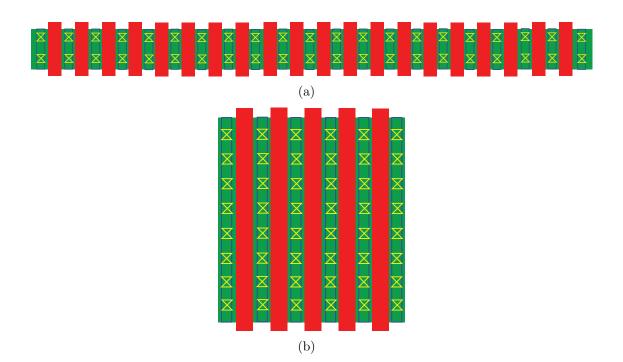

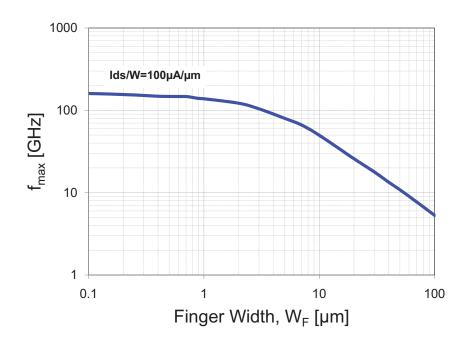

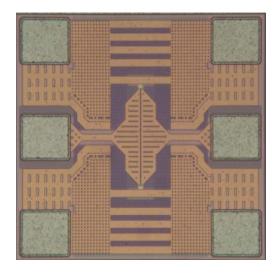

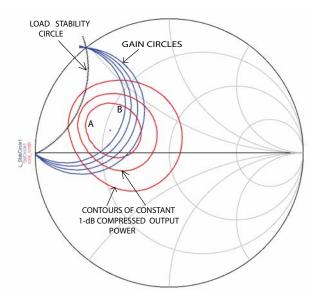

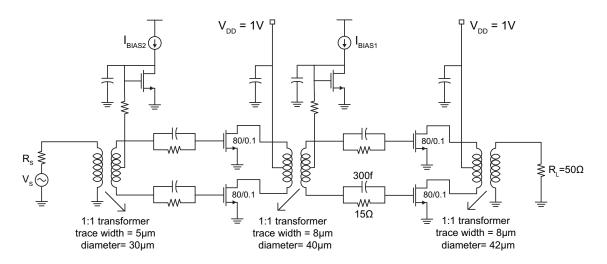

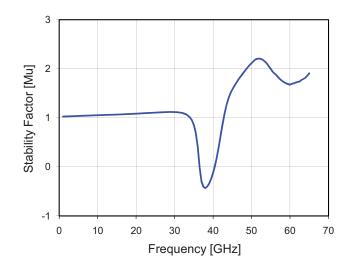

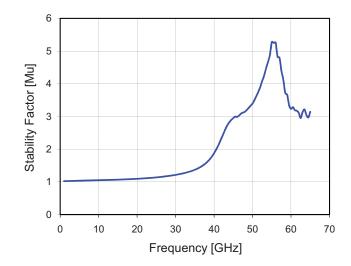

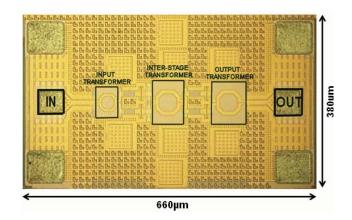

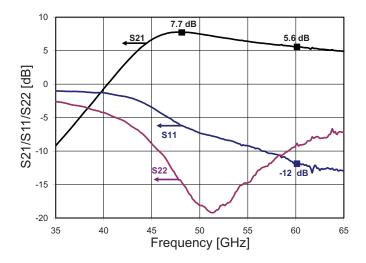

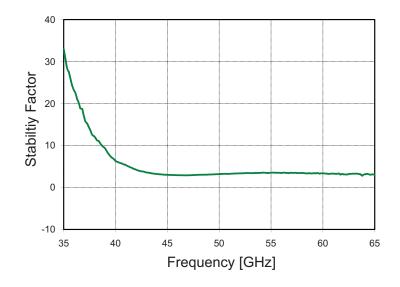

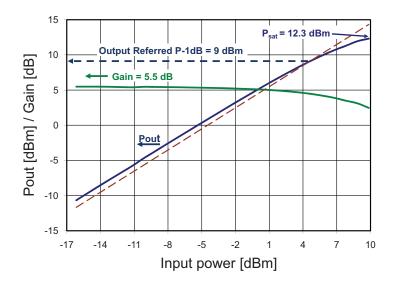

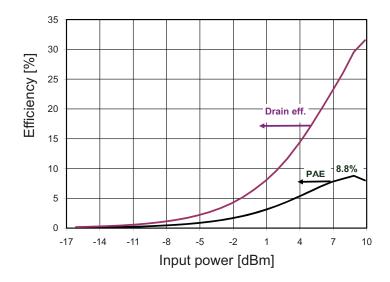

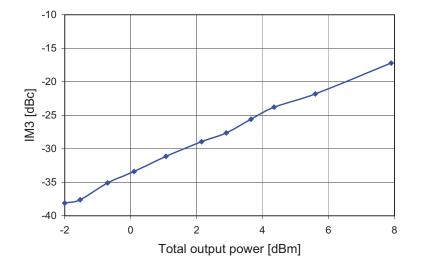

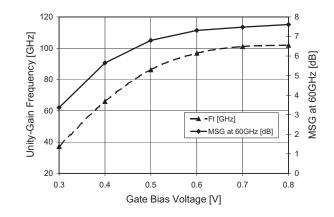

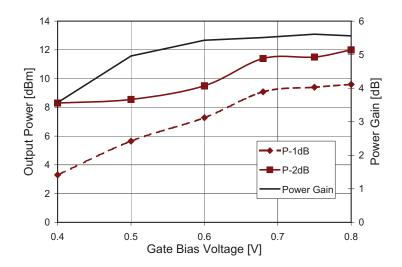

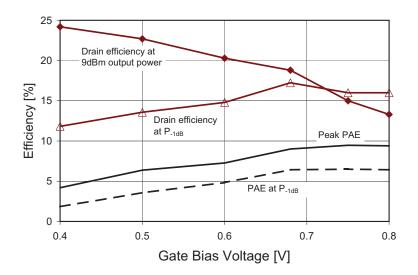

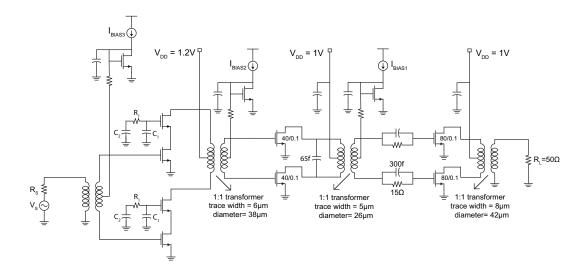

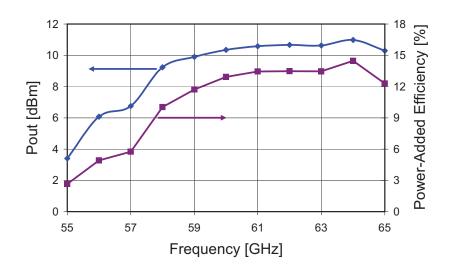

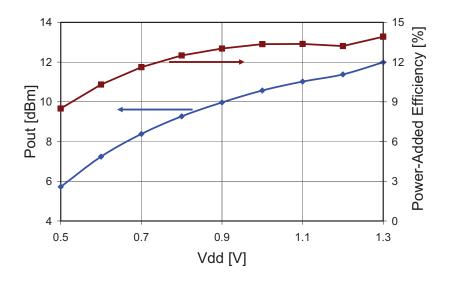

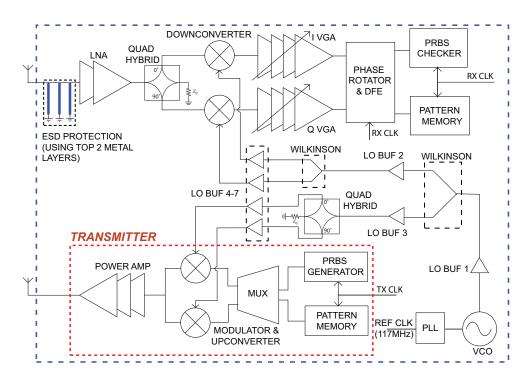

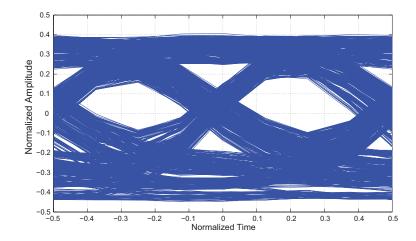

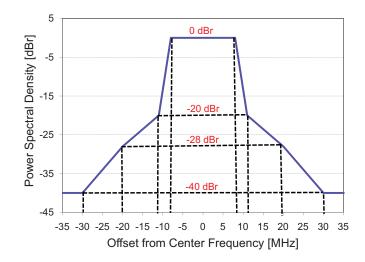

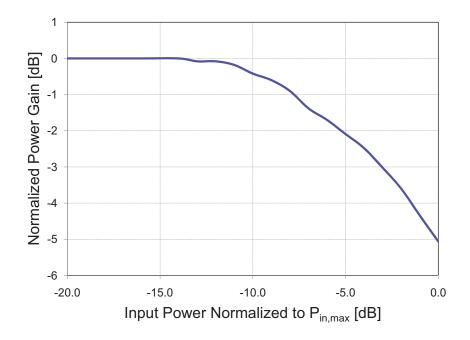

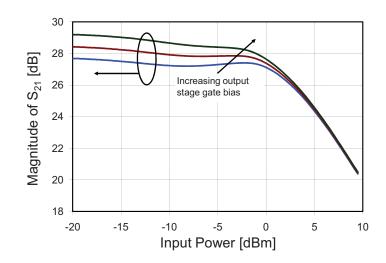

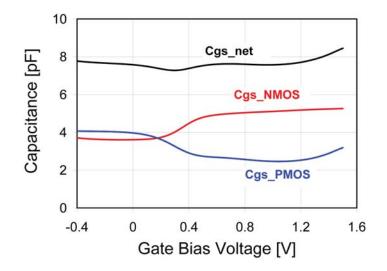

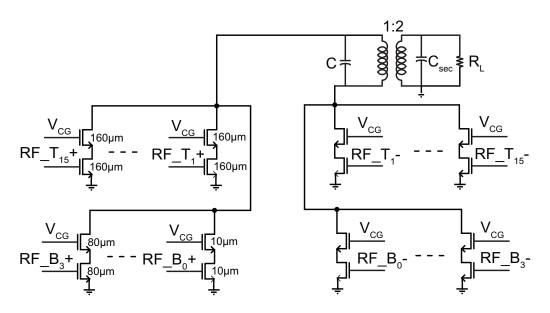

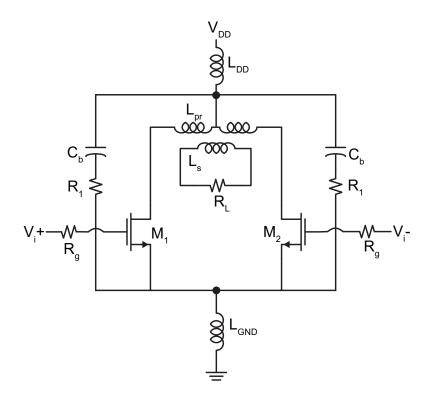

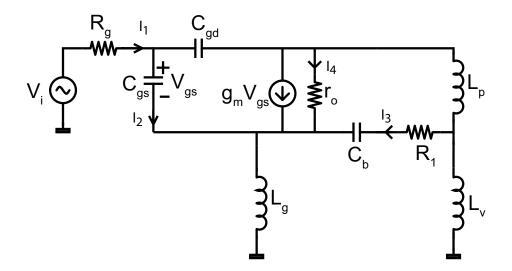

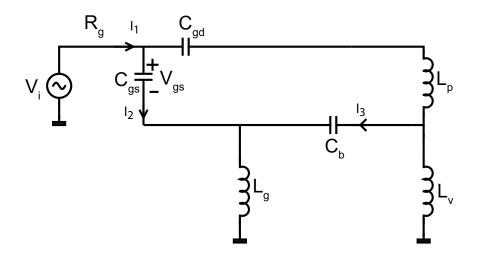

2.22 Layout of a conventional symmetric 2:1 transformer. . . . . . . . . . . . . . . . . 282.23 Current distribution in two parallel conductors carrying current in opposite directions. 282.24 Modified layout of a 2:1 transformer with parallel primary. . . . . . . . . . 292.25 Simulated insertion loss of parallel primary transformer. 30 2.26 Principle of transformer-based power combining. 31 33 2.28 Efficiency of the power combining network in the band of interest. 34 353.1Conceptual layout of a wide transistor employing a) multiple fingers  $(N_F)$  and smaller finger width  $(W_F)$  b) smaller number of fingers and larger finger width. 39 3.2 Dependence of  $f_{max}$  on device finger width at a given current density. . . . 403.3 41 Contours of constant 1-dB compressed output power, power gain and load 3.4 423.543 3.6 Schematic of a transformer-coupled two-stage 60 GHz power amplifier. . . . 443.7463.8 Simulated  $\mu$  factor for the 60GHz differential PA with RC stabilizing network. 473.9Chip micrograph of the transformer-coupled two-stage 60GHz PA. . . . . . 473.10 Measured small-signal performance of the two-stage 60GHz power amplifier. 483.11 493.12 Measured gain and output power of the two-stage 60GHz power amplifier. 49. 3.13 Measured efficiency of the two-stage 60GHz power amplifier. . . . . . . . . 503.14 Measured IM3 as a function of output power of the two-stage PA. . . . . . 503.15 Measured  $f_T$  and maximum stable gain (MSG) at 60 GHz for an 80 $\mu$ m transistor. 51 3.16 Measured output power ( $P_{-1dB}$  and  $P_{-2dB}$ ) and power gain for varying gate 523.17 Measured drain efficiency and power-added efficiency for varying gate bias of 533.18 Transformer-coupled three-stage PA schematic. 533.19 Measured output power versus frequency for the three-stage PA. . . . . . 543.20 Measured PA output power for different supply voltages. . . . . . . . . . . . 553.21 Block diagram of the 60GHz integrated transceiver. . . . . . . . . . . . . . . . . 553.22 Schematic of the quadrature modulator feeding the power amplifier. . . . . 563.23 Measured eye diagram when transmitting QPSK data. 574.160 Schematic of the two-stage transformer-coupled 2.4GHz PA. . . . . . . . 4.2Spectral mask specified by the 802.11g standard.... 61 4.363

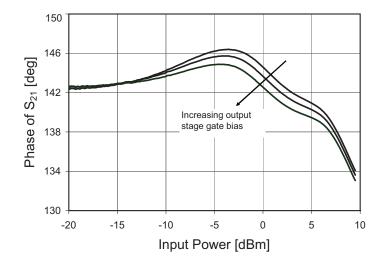

| 4.4  | Measured AM-AM response for different gate bias voltages at 2.4GHz 64                                    | 4 |

|------|----------------------------------------------------------------------------------------------------------|---|

| 4.5  | Simulated gate capacitance of NMOS, PMOS and total sum device 64                                         | 5 |

| 4.6  | Measured variation in phase of $S_{21}$ of the PA as a function of input power at                        |   |

|      | 2.4GHz with PMOS-based compensation scheme                                                               | 5 |

| 4.7  | Modified layout of a 2:1 power combiner                                                                  | 6 |

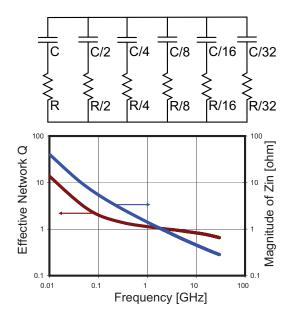

| 4.8  | Bypass network and its frequency response for C=100pF and R=10 $\Omega$ 6                                | 7 |

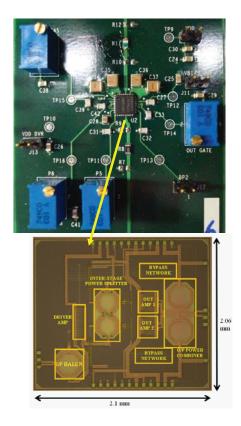

| 4.9  | Test FR4 board with the packaged chip and die micrograph of the PA 66                                    | 8 |

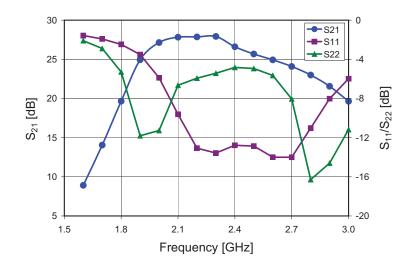

| 4.10 | Measured small-signal performance of the PA                                                              | 9 |

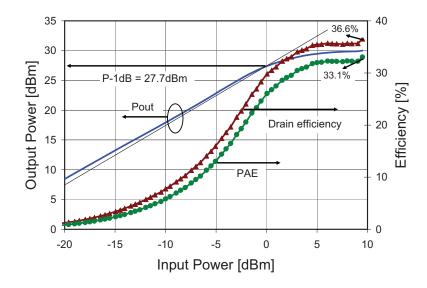

| 4.11 | Measured large-signal performance of the PA                                                              | 0 |

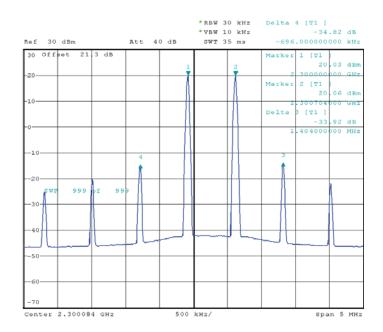

| 4.12 | Intermodulation distortion in a two-tone test with 1MHz tone spacing 70                                  | 0 |

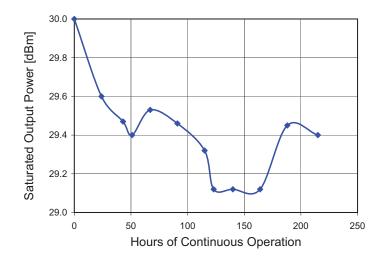

| 4.13 | Saturated output power of the PA as a function of time                                                   | 1 |

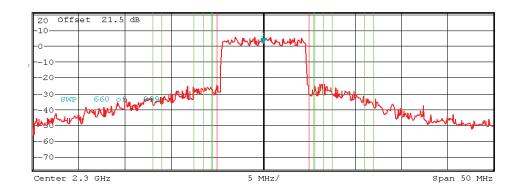

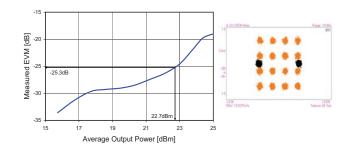

| 4.14 | Output spectrum of the PA excited with 802.16e mobile WiMax signal 7                                     | 1 |

| 4.15 | Measured EVM as a function of average output power                                                       | 2 |

| 4.16 | Transformer-based power combiner                                                                         | 3 |

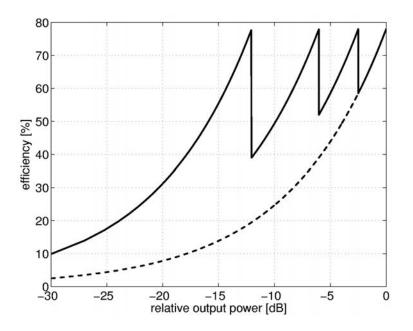

| 4.17 | Efficiency enhancement with power back-off                                                               | 3 |

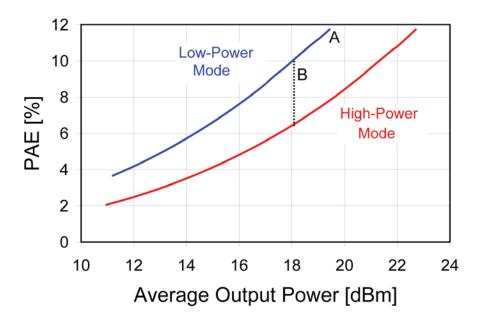

| 4.18 | Efficiency of the PA in low-power and high-power mode                                                    | 5 |

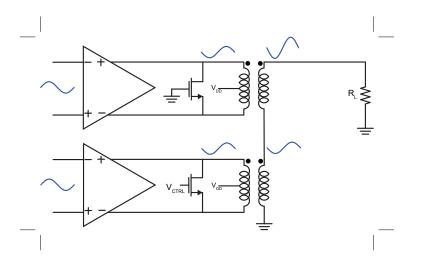

| 4.19 | Implementation of power back-off with shorting switches                                                  | 5 |

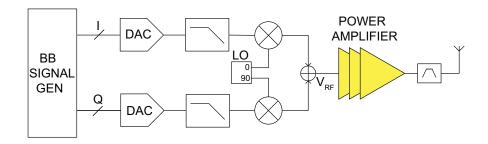

| 5.1  | Block diagram of a conventional wireless transmitter                                                     | 7 |

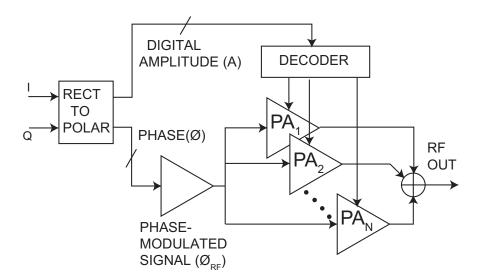

| 5.2  | A digitally-modulated polar power amplifier                                                              | 9 |

| 5.3  | The Class D power amplifier                                                                              | 0 |

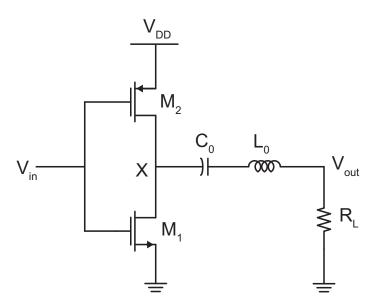

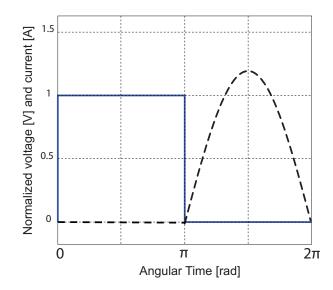

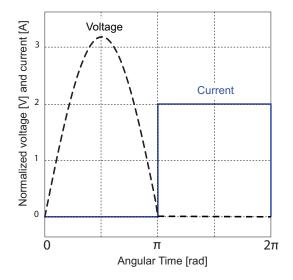

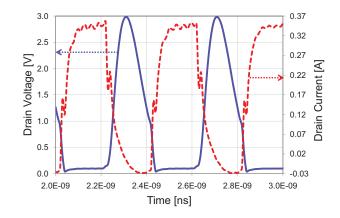

| 5.4  | Current and voltage waveforms in the Class D PA                                                          | 1 |

| 5.5  | The Class E power amplifier                                                                              | 1 |

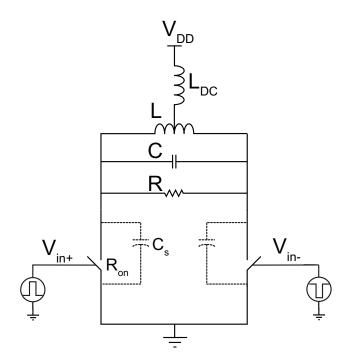

| 5.6  | The inverse Class-D $(D^{-1})$ power amplifier                                                           | 3 |

| 5.7  | Current and voltage waveforms in Class $D^{-1}$ PA                                                       | 3 |

| 5.8  | Efficiency of an ideal Class- $D^{-1}$ PA as a function of the loaded quality factor                     |   |

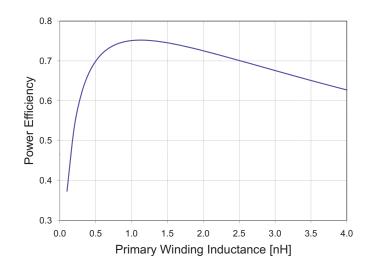

|      | of the <i>RLC</i> network. Here, the inductor is assumed lossless, and $Q = \omega \cdot R \cdot C$ . 84 | 4 |

| 5.9  | Efficiency of a 2:1 transformer at 2.4GHz as a function of primary winding                               |   |

|      | inductance                                                                                               | 5 |

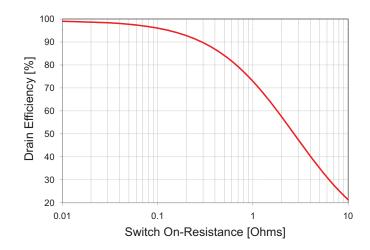

| 5.10 | Variation in PA efficiency as a function of the switch resistance                                        | 6 |

|      | Simulation setup of an ideal inverse-D PA                                                                |   |

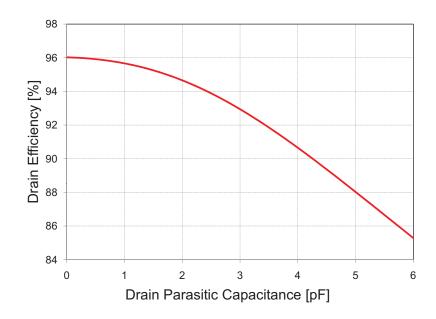

| 5.12 | Degradation in drain efficiency due to increased device parasitic                                        | 7 |

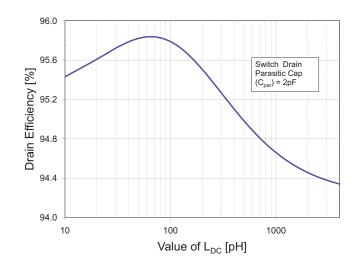

| 5.13 | Dependence of drain efficiency on DC feed inductance value, in presence of                               |   |

|      | finite drain parasitic capacitance                                                                       | 8 |

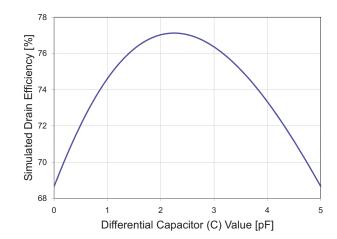

| 5.14 | Simulated drain efficiency of Class- $D^{-1}$ PA as a function of the parallel tuning                    |   |

|      | capacitor                                                                                                | 9 |

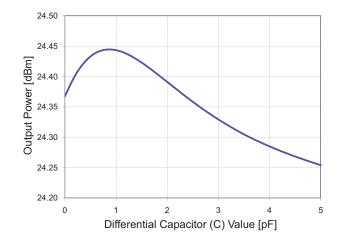

| 5.15 | Simulated output power of Class- $D^{-1}$ PA as a function of the parallel tuning                        |   |

|      | capacitor                                                                                                | 9 |

| 5.16 | Simulated drain voltage and current waveforms in CMOS Class- $D^{-1}$ PA 9                               | 0 |

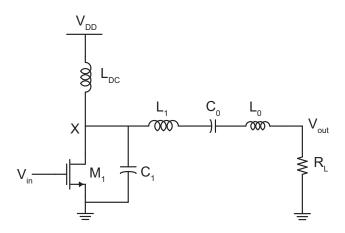

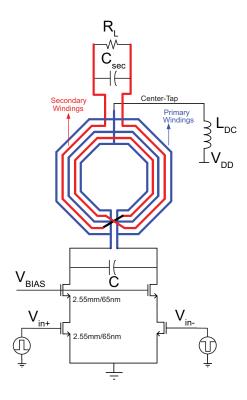

|      | Schematic of the transformer-coupled inverse-D PA                                                        | 1 |

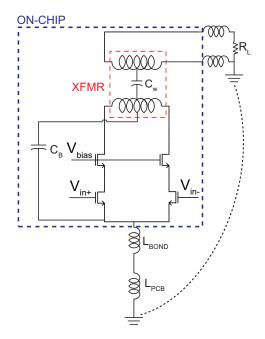

| 5.18 | Ground bounce in a transformer-coupled PA                                                                | 2 |

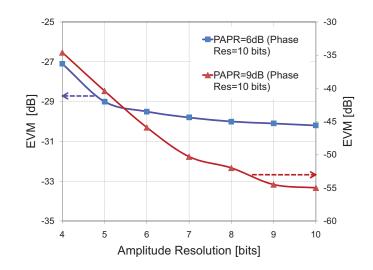

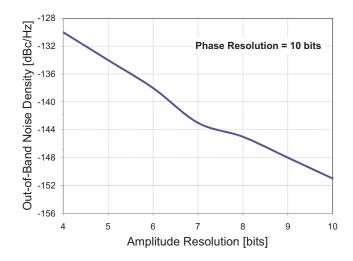

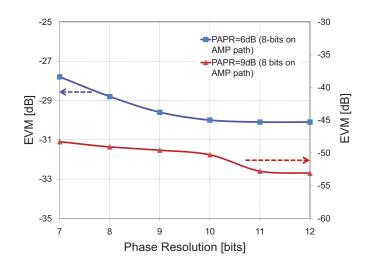

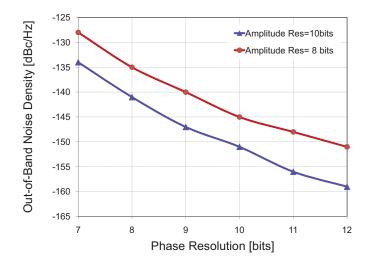

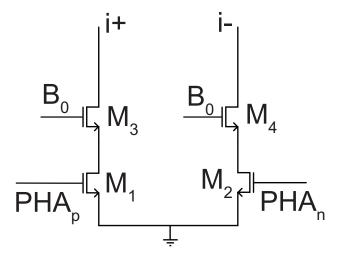

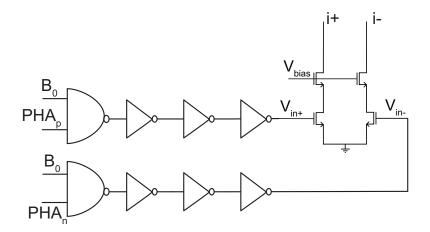

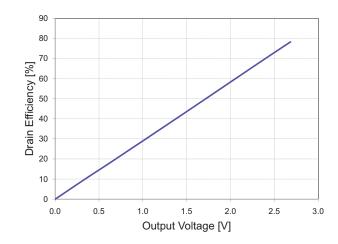

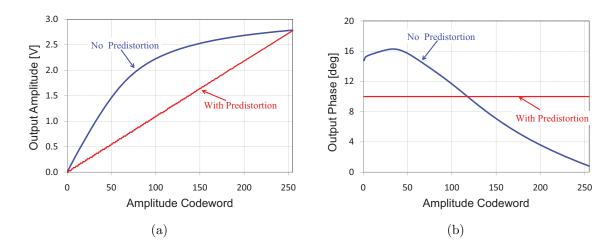

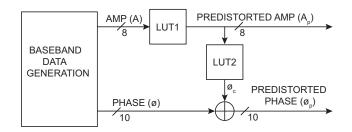

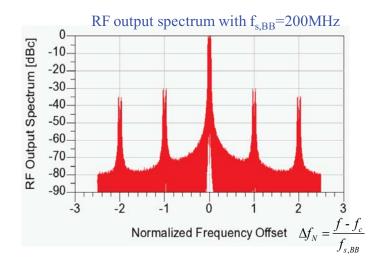

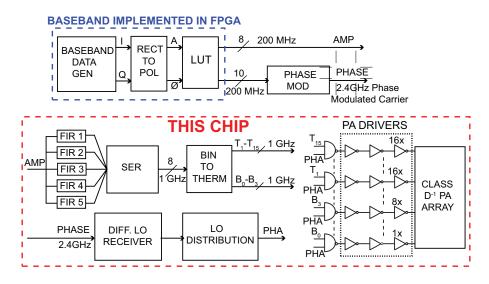

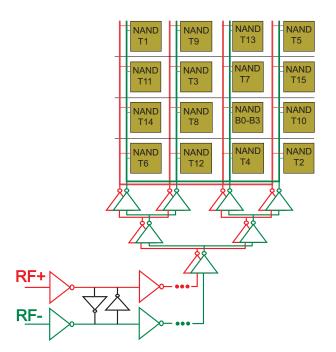

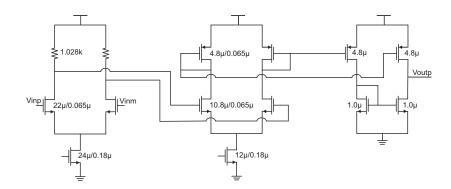

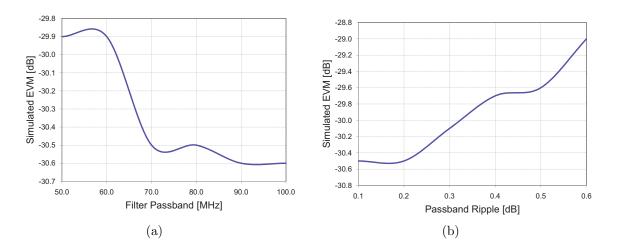

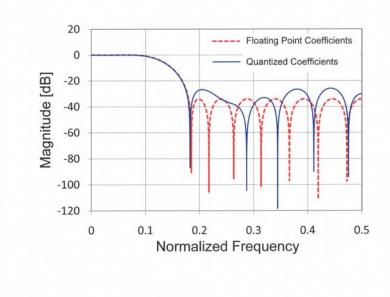

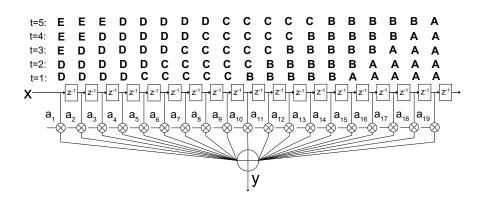

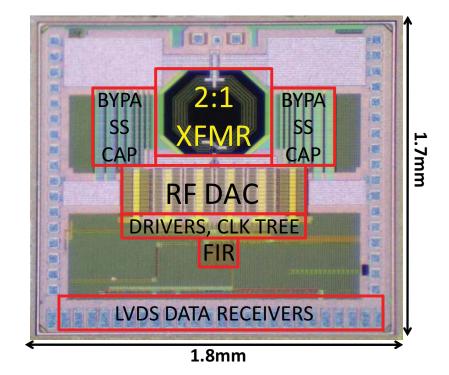

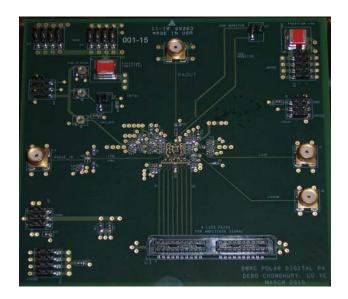

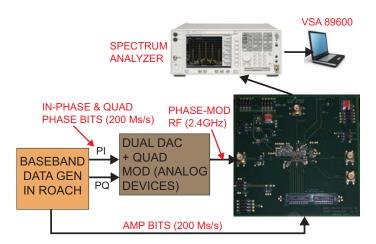

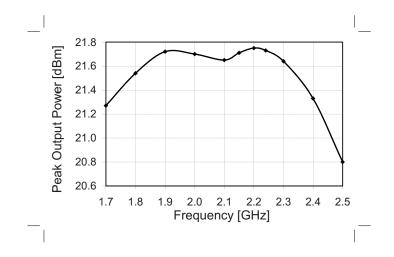

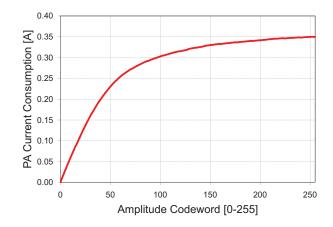

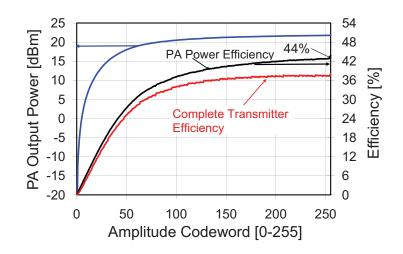

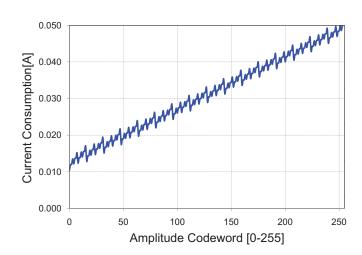

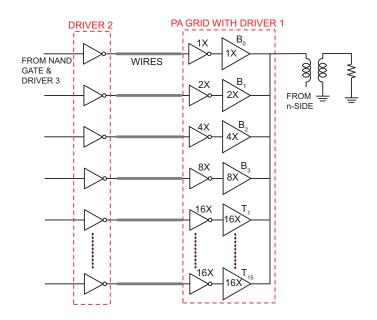

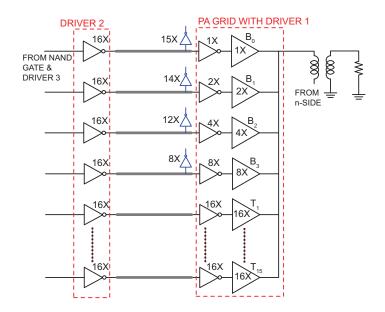

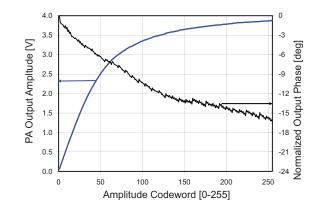

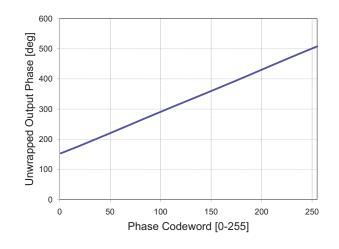

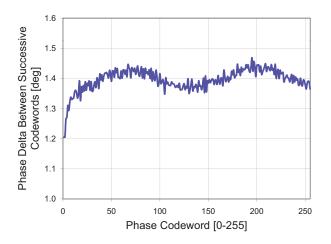

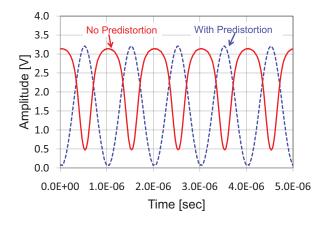

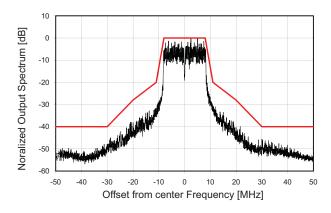

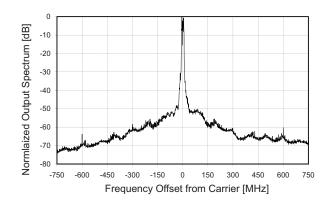

93 5.20 EVM of an ideal digitally-modulated transmitter while transmitting 802.11g 64QAM data. The variation in EVM is shown for two PAPR cases- 6 dB and 945.21 Variation in the noise density at 200MHz offset from the carrier as a function of the amplitude resolution (the phase path resolution fixed at 10-bits). . . . 955.22 EVM of an ideal digitally-modulated transmitter while transmitting 802.11g 60QAM data. The variation in EVM with the phase resolution is shown for two PAPR cases - 6 dB and 9 dB. 96 5.23 Variation in the noise density at 200MHz offset from the carrier as a function of the phase resolution (the amplitude path resolution fixed at 10-bits). . . . 96 975.25 Switching an unit cell on/off through the cascode gate. . . . . . . . . . . . . 985.26 Combining amplitude and phase information using digital NAND gates. . . 98 5.27 Linear back-off of drain efficiency with the output amplitude. . . . . . . . 99 5.28 Simulated linearity of the PA array: a) AM-AM response b) AM-PM response.101 5.29 Look-up table based static digital predistortion. . . . . . . . . . . . . . . . . . 1015.30 Simulated output spectrum with signal replicas at multiples of the baseband 1035.31 Block diagram of the mixed-signal polar transmitter. . . . . . . . . . . . . . . . 1045.32 Layout of the RF DAC.  $\ldots$ 1051055.34 Differential receiver for phase-modulated RF signal. . . . . . . . . . . . . . . . 1065.35 a) Effect of the filter passband on system EVM. Here, the filter passband ripple is assumed to be smaller than 0.3dB. b) Effect of the filter passband ripple on system EVM. Here, the filter passband is assumed to be 80MHz. 107 5.36 Simulated magnitude response of the filter with and without coefficient quan-1085.37 Concept of coefficient grouping in a parallelized FIR filter. . . . . . . . . 1095.38 Chip micrograph of the 65nm mixed-signal polar PA. . . . . . . . . . . . . . 111 111 1121135.42 Measured DC current consumption of the PA array. . . . . . . . . . . . . . . 1135.43 Measured PA output power, drain efficiency and transmitter efficiency at 2.25GHz for different amplitude codewords. 1145.44 Measured DC current consumption of the digital inverters. . . . . . . . . . 1151155.46 Low-skew layout technique for the PA array with drivers. . . . . . . . . . . 116117117

| 5.49 | Measured phase difference as the phase codeword is incremented               | 117 |

|------|------------------------------------------------------------------------------|-----|

| 5.50 | Effect of amplitude predistortion.                                           | 118 |

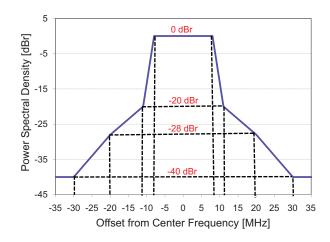

| 5.51 | Output spectrum when transmitting 802.11g 54Mbps 64-QAM OFDM data.           | 118 |

| 5.52 | Far out spectrum when transmitting WLAN data                                 | 119 |

| A.1  | Schematic of the output stage of the PA with bond-wire inductances and       |     |

|      | bypass capacitances.                                                         | 131 |

| A.2  | Small-signal representation of common-mode half-circuit of the PA            | 131 |

| A.3  | Small-signal representation of common-mode half-circuit of the PA under high |     |

|      | Q assumption.                                                                | 133 |

# List of Tables

| 3.1 | Link budget analysis for 2m communication at 60 GHz | 38  |

|-----|-----------------------------------------------------|-----|

|     | EVM requirements of WLAN 802.11g standard           | 93  |

| 0.2 | power amplifier                                     | 119 |

#### Acknowledgments

This work would not have been possible without the help and influence of many people. First, I would like to thank my advisor Prof. Ali M. Niknejad for his help and support. As a graduate student in a new country, there are many challenges that one needs to handle, in addition to academic work. I am thankful to my advisor for being understanding at all times and for helping me stay focused and motivated. I would like to thank Prof. Elad Alon for his extensive help and feedback. I would also like to thank Prof. Seth Sanders and Prof. Paul Wright for being on my qualifying exam committee.

I would like to take this opportunity to thank all of the people I have met and worked with at BWRC. I have learnt more here in the last few years than I could have ever imagined and a lot of it is due to my classmates and seniors at BWRC: Cristian Marcu, Amin Arbabian, Ehsan Adabi, Wei-Hung Chen, Mohan Dunga, Zhiming Deng, Ali Afshar, Jason Stauth and others. Whether its helping me with work or just offering a friendly advice, I could not have done it without all of your help. Working with juniors like Lu Ye, Jiashu Chen, Lingkai Kong, Chintan Thakkar, Maryam Tabesh and others has been an enriching experience as well. My collaboration with Lu Ye in designing the digital transmitter was particularly fruitful and enjoyable.

I would like to offer my special thanks to Peter Haldi, a visiting scholar at BWRC in 2006. Special thanks also goes to Dr. Patrick Reynaert, a post-doc in our group in 2007. We had a wonderful time talking about various details and I got to learn a lot from him.

Finally, I would like to acknowledge the love and support of my parents Suprita and Bijan. Without their love and encouragement, I would have never been where I am now. Special thanks goes to my wife Souti for all her patience, love and encouragement. She always helped stay motivated during the tiring tapeout and measurement phases. Thanks to my sister Debjani for her love. Thanks a lot and this thesis is to you all.

# Chapter 1 Introduction

The last decade has witnessed phenomenal growth of the wireless industry, and wireless connectivity has now reached a state where it is considered to be an indispensable service. A vast plethora of applications such as mobile internet, gaming, home networking, and multimedia streaming have motivated the growth of high data rate wireless communication systems. A plot highlighting the increasing demand for high data rate communication both for long-range (cellular) and short-range (like WLAN, Bluetooth etc) applications is shown in Fig. 1.1 [1]. Similarly, as depicted in Fig. 1.2, the demand for converged wireless devices like smartphones and PDAs has been growing year after year [2].

Driven by the need for higher data-rates, standards have evolved towards packing more bits per second per Hertz by using higher order modulation. Newer standards are also being developed that seek to utilize higher bandwidths, like the 7GHz of unlicensed bandwidth around 60GHz. Standards such as 802.11ad and WiGig are targeting this mm-wave band to create very high data rate short-range wireless personal area networks (WPANs) [4].

These trends towards ubiquitous, high data-rate wireless connectivity and highly integrated solutions have opened up a new wave of challenges and opportunities for RF (radiofrequency) and mm-wave integrated circuit design. Mobile terminals inherently operate on batteries having limited charge, and hence power-efficiency is one of the key metrics [5]. In addition, small form-factor, low-cost, and reliability are key characteristics of radios used in portable devices.

Most of the power dissipation in mobile wireless products is due to the transmitter, and specifically, due to the power amplifier (PA). The PA, which is the last building block in a conventional transmit chain (as shown in Fig. 1.3), is often times the most power-hungry. This is because the PA needs to deliver several tens to hundreds of milliwatts to a fixed load (like the antenna) and thus its power efficiency significantly impacts the battery life of a mobile device. In addition, PAs are often implemented as multi-stage designs, requiring a large number of passive elements (like inductors, capacitors, transmission lines etc.) for interstage matching. These passives consume significant area, increasing the die size and cost. This naturally leads to the conclusion that increasing the power efficiency while reducing

Figure 1.1: Growth of high data rate wireless communications [1].

Figure 1.2: Growth in the sale of Nokia converged devices (smartphones) [2].

Figure 1.3: Block diagram of a wireless transmitter.

the size and cost of the power amplifier in particular - and the transmitter in general- is a key challenge in the evolution of mobile wireless transceivers.

One of the most effective ways to achieve compactness and reduce cost is a high level of integration. Integration of multiple circuit blocks into a single chip would reduce the size of the final product, the number of packages required, packaging and testing costs and printed circuit board footprint [5]. Thus, there has been tremendous effort by both industry and academia to realize a true single-chip radio in CMOS technology.

Over the last decade, most of the building blocks of an RF transceiver have been successfully integrated into CMOS technology. However, one piece that is missing from the puzzle is the power amplifier. The PA is often implemented as a stand-alone module in expensive processes like GaAs HBT (heterojunction bipolar transistors) in conjunction with external passives. The primary reasons for these are the high output power and power efficiency required by the PA, which are difficult to achieve in silicon based technologies. Although technology scaling typically provides faster transistors every generation, the breakdown voltage of the transistors also reduces every technology node. Thus, the power supply voltage needs to scale, making high power generation in silicon extremely challenging. In addition, on-chip passives suffer from low quality factor due to thin metals as well as the conductive nature of the silicon substrate. These losses degrade both the output power and efficiency of the PA. The design of a fully-integrated power amplifier thus remains a complex challenge. The primary goal of this thesis is to investigate efficient, integrated transmitter design, with special emphasis on integrated power amplifier design in nanoscale CMOS technology.

Since they play a crucial role in PAs, we will begin by exploring the design of passive matching networks. Matching networks are required for performing impedance transformation at the output of the PA. The PA needs to interface with a fixed external load like the filter or the antenna (which are often times 50 $\Omega$ ). If there is no matching network in between the PA and the fixed load, the output power that can be delivered to the load is limited. For example, a PA operating from a 1-V supply can deliver no more than 10dBm into a 50 $\Omega$  load. To increase the output power beyond this, a matching network is required which will transform the 50 $\Omega$  impedance to a lower value.

Such matching networks typically consist of passive components like inductors and capacitors which have finite quality factors. Hence matching networks are fundamentally lossy circuits. In PA applications, low insertion loss of the matching network is highly desirable since this loss directly degrades both the output power and the power efficiency of the PA. Furthermore, it is desirable to minimize the area of the passive components in a fully-integrated design.

The conventional way of performing such an impedance transformation is by using 'LC' matching networks [6]. However, it has been shown in [7] that the insertion loss of an 'LC' matching network increases rapidly as the impedance transformation ratio (ITR) is increased. This is clearly a problem in low-voltage high output power PA design because of the required high impedance transformation.

Transformers using coupled inductors are another class of impedance transformation circuit. It has been shown in [7] that transformers can ideally break the efficiency-ITR trade-off inherent in 'LC' matching networks. Hence, transformers have recently become popular at RF frequencies [8] and their application in PA design has also been demonstrated [9] [10] [11].

In this work, we want to extend the operating regime of transformers to mm-wave frequencies (specifically to 60GHz). Most of the reported circuits at mm-wave frequencies employ distributed matching networks using transmission lines [12] [13] [14] [15]. Such matching networks are easier to model, but are bulky and occupy large area, even at 60GHz. In contrast, we will demonstrate in Chapter 2 that by choosing an appropriate size and geometry, it is feasible to design a low-loss, compact transformer even at 60GHz. The small size of such transformers is a clear win over the distributed matching networks.

In order to utilize these transformers to design efficient power amplifier circuits, a simple, scalable model needs to be developed. The conventional way of modeling a transformer is by using lumped elements [16] [17]. We will show in Chapter 2 that such a lumped element model of the transformer can predict its performance faithfully even up to mm-wave frequencies. Despite its accuracy, the lumped model suffers from the fact that it employs many parameters - some of which can be predicted by analytical equations but some need to be fitted based on simulations. Thus it is challenging to make such a model truly scalable with transformer size and hence difficult to use during circuit design.

In this work, we propose a distributed modeling methodology for on-chip transformers. Utilizing transmission-line equations, we will show that we can predict the insertion loss and impedance transformation ratio of the transformer over a wide range of frequency. The proposed model has far fewer parameters and is also length-scalable, making it useful during the design phase of the PA.

In order to verify the utility of the designed transformers and the proposed modeling method, a 60GHz fully-integrated, transformer-coupled power amplifier will be presented in Chapter 3. It will be shown that in addition to performing impedance transformation, transformers offer additional benefits in PA design like differential-to-single ended conversion and convenient biasing through the center tap of the winding. A systematic design methodology will be developed to facilitate the co-design of PAs and transformers. Utilizing this algorithm, a two-stage as well as a high-gain three stage power amplifier will be demonstrated in 90nm CMOS technology. Operating from a 1V supply, this PA delivers more than 12dBm of output power, which is one of the highest reported for a 60GHz CMOS PA without power combining. The compact size of the reported PA clearly shows the area benefit of transformers at these frequencies.

The design and modeling of transformers developed in this work is also useful at RF frequencies. However, the output power requirements in the low-GHz wireless systems is often higher as they are meant for long-range communication. In low voltage CMOS process, higher output power generation translates to a higher impedance transformation ratio in the output matching network. An efficient way to realize such a high transformation ratio with low insertion loss is to use power-combining.

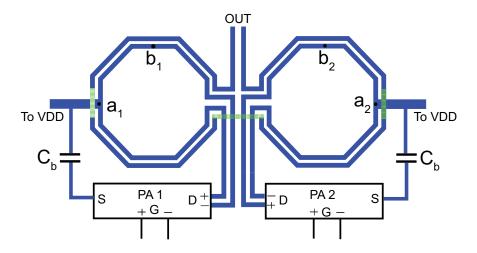

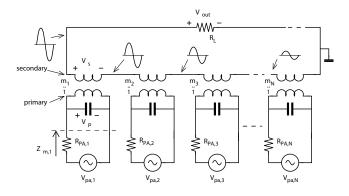

Different types of power combining architectures have been proposed in literature [18] [19]. Aoki *et al* [7] proposed a novel on-chip impedance matching and power-combining method called the distributed active transformer (DAT). It combines several low-voltage differential amplifiers efficiently with their outputs in series to produce a larger output power while maintaining a 50 $\Omega$  match. However, in the original design, the amplifiers driving the DAT were not independent of each other and hence individual amplifiers could not be turned off when less output power was required. [20] proposed a modified version of the DAT where individual 1:1 transformers were cascaded in series to realize an on-chip power combiner. While similar in principle to the DAT operation, the power combiner in [20] allowed independent amplifiers to be turned off. In this thesis, we have adopted a similar power combiner architecture to generate high output power at RF frequencies. A modified layout strategy that can ensure better PA linearity will be discussed in Chapter 4.

Indeed, the linearity of the power amplifier is becoming increasingly important in newer wireless systems. The use of higher order modulation like 64-QAM, often coupled with OFDM (orthogonal frequency division multiplexing), leads to very high dynamic range signals. Processing such signals with high integrity while delivering high output power poses a significant challenge for the PA. Some of the older wireless standards like GSM employed constant envelope modulation and hence linearity was not the chief concern. Consequently many of the original CMOS power amplifiers published in literature were switching PAs [21] [22]; in fact, the original PA using the DAT [23] was also such a switch-mode. Because of the evolution of wireless standards employing both amplitude and phase modulation, it is only more recently that PA linearity requirements have become so stringent.

There has been a lot of work to improve the linearity of the power amplifier [24] [25] [26]. In this thesis, we have tried to come up with simple circuit techniques that can increase the linearity of the core PA block. We have analyzed the desired amplitude and phase response that allows the PA to meet the linearity requirements with the maximum efficiency. We will show in Chapter 4 that the choice of an optimal gate bias for the output stage, together with capacitive phase compensation, can enable a highly-linear PA design without sacrificing efficiency. Additional linearization techniques like those proposed in [24] and other work can

be applied to further improve the linearity.

In order to verify the effectiveness of our proposed scheme, a two-stage 2.4GHz Class-AB power amplifier has been fabricated in 90nm CMOS technology. Transformer-based power combining has been used for the matching network design. With 37% efficiency, the PA delivers more than 1W of output power, which is one of the highest reported in literature for a linear CMOS PA. The PA can meet the linearity requirements of modern wireless standards like WiMAX with 18% efficiency.

It is well-known that there exists a fundamental linearity-efficiency trade-off in conventional power amplifier design. We have shown in Chapter 4 that PAs like Class A/AB/B can achieve high linearity with proper design. However, the efficiency of such PAs is fundamentally lower than that of switching power amplifiers like Classes D/E/F [27]. Unfortunately, traditional transmitter implementations (Fig. 1.3) do not allow the use of such switching PAs in systems that employ amplitude modulation. Therefore, numerous methods have been proposed to either improve the efficiency of linear amplifiers or linearize the more efficient nonlinear amplifiers without significantly degrading their efficiency.

One such technique is envelope-elimination and restoration (EER) and is based on performing efficient constant-envelope amplification of the phase-modulated portion of the input signal and then restoring the envelope by amplitude modulation at the output [28]. In effect, an EER system is a polar transmitter in which the signal is decomposed into a constant-envelope RF phase-modulated signal and an envelope component. Several papers have demonstrated the suitability of such architectures for CMOS implementation [29] [30]. However, the efficiency-bandwidth trade-off in analog supply modulators has restricted the popularity of this architecture to relatively narrowband modulation standards.

In order to expand such a polar architecture to wideband systems such as 802.11g, 802.11n, and others, in this thesis we study a mixed-signal polar transmitter in 65nm CMOS technology. The proposed architecture does not employ a supply modulator but instead operates the power amplifier as an RF-DAC. The phase-modulated signal being constant-envelope, the core PA can still be efficient but non-linear (from the standpoint of amplitude modulation); the amplitude information is transmitted by turning on and off an appropriate number of unit cells.

In addition to allowing the use of a non-linear, efficient PA, such a mixed-signal architecture also requires less passive matching networks. This is important because the passives do not scale well with technology and hence in a multi-stage PA the area is often dominated by the passive elements. A truly scalable architecture, which will benefit from technology scaling like digital circuits, is thus highly desirable for low-cost wireless solutions. A mixed-signal polar architecture offers such a potential.

Some previous publications have discussed the concept of such a digitally modulated transmitter [31] [32] [33] [34]. However, not much attention has been paid on the design of a high output power, high efficiency, fully integrated switching PA. For example, [31] uses a Class-A amplifier as the unit cell. But, it would be much more efficient to use switching PAs in such an architecture. [32] proposes the use of Class-E power amplifiers. However, the

targeted output power level is much lower and the amplifier basically acts as a PA driver. There is thus little work done on a detailed study of this digital polar architecture with an emphasis on an efficient, high-power, fully-integrated PA design. The real benefit of such a mixed-signal transmitter can be leveraged only if the PA is more efficient that what can be achieved by a linear amplifier like the one designed in Chapter 4. The core PA design is thus an integral part of such a transmitter.

This thesis therefore proposes the use of an efficient, switching inverse Class-D PA as the core of such a mixed-signal system. We will analyze its advantages, design methodology, linearity, and back-off characteristics in details in Chapter 5. The power of digital signal processing will be leveraged to compensate for the PA non-idealities.

The other piece missing from previous digitally modulated transmitter designs is a consideration of the out-of-band noise for co-existence issues. Meeting the spectral mask specified by the standard is a necessity; however, care also needs to be taken to ensure that the far out-of-band noise is low enough so that it does not desensitize the receiver of another radio in a multi-standard solution. In this work, we have analyzed the required amplitude and phase path resolution to meet not only the linearity requirements, but also to ensure low out-of-band noise. Furthermore, we will be demonstrate the design of a low-power interpolation filter that can be used to prefilter any replicas of the baseband signal that remain after oversampling.

A prototype of this mixed-signal transmitter with integrated filtering has been fabricated in 65nm CMOS technology. The PA achieves about 22dBm of output power with over 44% efficiency. It requires only one transformer in the whole design, even though it has an effective power gain of more than 30dB. As will be presented in Chapter 5, the performance of the designed transmitter is even comparable to some commercial power amplifiers implemented in expensive compound semicondcutor processes.

### Chapter 2

## Passive Matching Networks for Power Amplifier Design

In the previous chapter, passive matching networks were identified as one of the key blocks enabling an efficient, low-voltage power amplifier in CMOS technology. Because lossless reactive components do not exist, all impedance matching networks will have some insertion loss. These losses can be quite pronounced in PAs since they directly degrade the efficiency. This issue is even more serious when designing PA with state-of-the-art lowvoltage CMOS technologies because of the high required impedance transformation ratio and the lossy on-chip passive components. Two different types of matching networks have been used mostly in PA design: LC resonant matching networks and transformer-based matching networks. In this chapter, the benefit of transformers vis-a-vis conventional LC matching networks will be elaborated. Specific design examples for low-loss RF and 60GHz transformers will be presented, and a simplified modeling method for on-chip transformers as power combiners to build high output-power amplifiers in low-voltage CMOS process.

### 2.1 LC Matching Networks

LC resonant matching networks are straightforward to implement. A single stage L-match is shown in Fig. 2.1, consisting of a capacitor and an inductor. A lossy inductor can be analyzed as a series equivalent circuit or a parallel equivalent circuit by adding a resistor to model the loss (Fig. 2.2) [35], where

$$Q_L = \frac{\omega L_s}{R_s} \tag{2.1}$$

$$R_p = R_s(Q_L^2 + 1) \tag{2.2}$$

$$L_p = L_s \frac{Q_L^2 + 1}{Q_L^2} \approx L_s \tag{2.3}$$

Figure 2.1: A single stage "L-match" with a series capacitor and a parallel inductor.

Assuming that at the frequency of interest  $L_p$  and C resonate with each other, it can be shown that

$$Q_{network} = \frac{R_p || R_L}{\omega L_p} = \frac{R_L}{\omega L_p + \frac{R_L}{Q_L}}$$

(2.4)

$$R_{in} = Re(Z_{in}) = \frac{R_p || R_L}{1 + Q_{network}^2} = \frac{1}{1 + Q_{network}^2} \cdot \frac{R_L}{1 + \frac{R_L}{\omega L_p Q_L}}$$

(2.5)

The impedance transformation ratio (ITR) is given by:

$$ITR = \frac{R_L}{R_{in}} = \frac{R_L}{R_p ||R_L} (1 + Q_{network}^2) = (1 + \frac{R_L}{\omega L_p Q_L}) (1 + Q_{network}^2)$$

(2.6)

The above equation shows that as the impedance transformation ratio increases, the  $Q_{network}$  also increases. This has an impact on the network efficiency as shown next.

The efficiency of a matching network can be calculated as the ratio of the power delivered to the load to the power delivered into the network. The efficiency  $(\eta)$  can be computed as

Figure 2.2: Equivalent models of an inductor with quality factor  $Q_L$ .

Figure 2.3: Single stage L-match network with inductor loss.

[7]

$$\eta = \frac{P_{out}}{P_{in}}$$

$$= \frac{|V_l|^2 / (2R_L)}{|V_l|^2 / (2(R_p)|R_L))}$$

$$= \frac{1/R_L}{1/R_L + 1/R_p}$$

$$= \frac{1}{1 + \frac{R_L}{\omega L_p Q_L}}$$

(2.7)

Equations 2.6 and 2.7 can be solved for  $\omega L_p$  in terms of the desired impedance transformation ratio (ITR), load resistor  $(R_L)$ , and inductor quality factor  $(Q_L)$ .

$$\omega L_p = \frac{R_p}{Q_L} = \frac{2(Q_L + 1/Q_L)}{ITR - 2 + \sqrt{ITR^2 + 4Q_L^2(ITR - 1)}} \cdot R_L$$

(2.8)

The efficiency of the network can be simplified in terms of ITR and  $Q_L$  by substituting Eq. 2.8 in Eq. 2.7.

$$\eta = \frac{1 + Q_L^2}{Q_L^2 + \frac{ITR + \sqrt{ITR^2 + 4Q_L^2(ITR - 1)}}{2}} \approx \frac{1}{1 + \frac{ITR}{Q_L^2}}$$

(2.9)

The efficiency of the LC matching network is plotted in Fig. 2.4 for different inductor quality factors. As seen from the plot, for a given inductor quality factor, the power efficiency drops quickly as ITR increases. The reason for this is that in the resonant network,  $Q_{network}$  times higher energy circulates in the LC tank than the energy delivered to the load [35]. As ITR increases,  $Q_{network}$  increases, so more energy is dissipated in the lossy inductor. This is a fundamental problem in PA design, since higher impedance transformation is required for low-voltage operation. This problem can be partially mitigated using multi-stage matching networks, but at the expense of higher passive component count and higher silicon area.

Figure 2.4: Efficiency of an LC matching network for different inductor quality factors.

### 2.2 Transformer-Based Matching Networks

Transformers- as their name implies- are another class of impedance transformation network. In this section, we will demonstrate that transformers, to first order, can overcome the ITR - efficiency tradeoff fundamental to LC matching networks. This is the reason why transformers have recently attracted interest from the power amplifier design community.

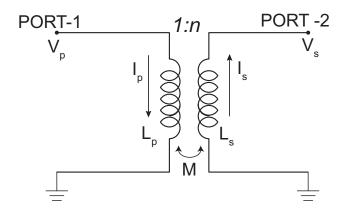

Transformers are based on the principle of electro-magnetic induction. In silicon, a transformer is implemented by two coupled inductors [36]. In a coupled-inductor transformer (Fig. 2.5), the magnetic field created by primary inductor  $L_p$  generates a voltage in the secondary inductor  $L_s$ . At the same time, the current through the secondary winding  $I_s$  will magnetically induce a voltage in the primary circuit. The port voltages of the transformer  $V_p$  and  $V_s$  in Fig. 2.5 are related to its port currents through

$$\begin{bmatrix} V_p \\ V_s \end{bmatrix} = \begin{bmatrix} j\omega L_p & -j\omega M \\ j\omega M & -j\omega L_s \end{bmatrix} \cdot \begin{bmatrix} I_p \\ I_s \end{bmatrix}$$

(2.10)

$$M = k \cdot \sqrt{L_p L_s} \tag{2.11}$$

$$n = \sqrt{\frac{L_p}{L_s}} = \frac{I_p}{I_s} = \frac{V_s}{V_p} \tag{2.12}$$

where M is the mutual inductance, k is the coupling factor, and n is the turn ratio between the primary and secondary windings. Due to the finite quality factor of on-chip inductors

Figure 2.5: Ideal transformer model.

and the non-unity coupling between primary and secondary windings, a real transformer deviates from the ideal equations described above. Fig. 2.6 shows a simplified model of a real transformer, where  $Q_p$  and  $Q_s$  represent the quality factor of the primary and secondary windings,  $R_L$  is the load resistance and  $C_p$  is the shunt tuning capacitance. We can convert

Figure 2.6: Simplified model of a 1:n transformer.

the shunt capacitor-resistor network into an equivalent series network given by [37]

$$R_{eq} = \frac{R_L}{1 + (\omega R_L C_p)^2}$$

(2.13)

$$C_{eq} = \frac{1 + (\omega R_L C_p)^2}{\omega^2 R_L^2 C_p}$$

(2.14)

The efficiency  $\eta$  of the transformer can be written as

$$\eta = \frac{P_{load}}{P_{load} + P_{diss}} \tag{2.15}$$

13

where  $P_{load}$  and  $P_{diss}$  are the power delivered to the load and power dissipated in the parasitic resistance of the transformer. Calculating the values of  $P_{load}$  and  $P_{diss}$  from the circuit and putting them in the above equation, the value of efficiency can be simplified to

$$\eta = \frac{\frac{1}{1 + (\omega R_L C_s)^2} R_p}{\frac{1}{1 + (\omega R_p C_p)^2} R_p + R_s + \left| \frac{Z_s + j\omega k L_p}{j\omega k L_p} \right|^2 R_p}$$

(2.16)

where  $Z_s$  is the secondary side impedance transformed to the primary side, as shown below.

$$Z_s = \frac{R_s + j\omega(1-k)L_s + \frac{1}{j\omega C_{eq}} + R_{eq}}{n^2}$$

(2.17)

The efficiency will be maximized if

$$\omega L_s = \frac{1}{\omega C_{eq}} \tag{2.18}$$

assuming  $L_p \simeq L_s/n^2$ . This gives a design equation which says that the optimum value of  $C_{eq}$  is one that tunes out  $L_s$  and not  $(1-k)L_s$ , as might appear from a first look at the equivalent circuit of Fig. 2.6. Basically, this condition minimizes the current  $I_1$  through  $R_p$  and its dissipated power by resonating inductors  $(1-k)L_s/n^2$  and  $kL_p$  with the capacitor  $C_{eq}$ . Note that because we use shunt tuning and not series tuning, the value of the tuning capacitor depends on the load resistor, even for a fixed size transformer at a given frequency.

In order to find the optimum winding inductance, we can take the derivative of the efficiency with respect to  $L_p$  and set  $\frac{\partial \eta}{\partial L_p}$  to zero [7]. This gives an optimum inductance value of

$$\omega L_p = \frac{\alpha}{1 + \alpha^2} \frac{R_L}{n^2} \tag{2.19}$$

where

$$\alpha = \frac{1}{\sqrt{\frac{1}{Q_s^2} + \frac{Q_p}{Q_s}k^2}}$$

(2.20)

and  $Q_p$  and  $Q_s$  represent the quality factor of the primary and secondary windings.

Using this optimum inductance and writing the parasitic winding resistances using winding quality factor (Q), the optimum efficiency is [7]:

$$\eta_{max} = \frac{1}{1 + \frac{2}{Q_p Q_s k^2} + 2\sqrt{\frac{1}{Q_p Q_s k^2} (1 + \frac{1}{Q_p Q_s k^2})}}$$

(2.21)

The above equation shows that the passive efficiency  $(\eta)$  can be maximized using a k as close as possible to unity. This is because the smaller the k, the larger is the fraction of the primary inductor current  $I_1$  that will go through the magnetizing inductor  $kL_p$ . This reduces the power that is delivered to the load resistor. More importantly, unlike LC matching networks,

Figure 2.7: Transformer efficiency for different primary and secondary winding quality factors for a) k = 0.4 b) k = 0.6 c) k = 0.8 and d) k = 1.0.

the transformer efficiency, to first order, is not affected by the transformation ratio, as seen from Eq. 2.21.

In addition to impedance transformation with low insertion loss, transformers also allow easy DC biasing using center taps of windings and inherently perform differential-to-single ended conversion for interface to external filters or the antenna. These features have made transformers attractive for power amplifier design in CMOS technology.

### 2.3 Transformers at 60GHz

Transformers have gained some attention at lower GHz RF frequencies, but their use in mmwave circuit design had not been demonstrated until recently [38]. Traditional microwave circuits employ distributed elements like microstrip lines, coplanar waveguides etc. to perform impedance transformation [3] [12] [14]. However, even at 60GHz, such transmission lines are bulky and increase silicon area, thereby incurring higher cost. Furthermore, they tend to be lossy at these frequencies due to the semi-conducting nature of the silicon substrate.

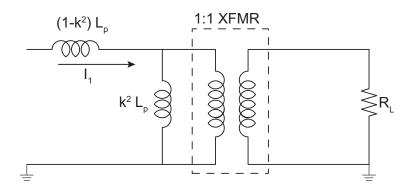

We have already seen that transformers fundamentally can perform impedance transformation as well as differential-to-single ended conversion. They are also very compact at mm-wave frequencies. In order to understand why transformers can be made much smaller in size at 60GHz, let us take a look at the equivalent circuit of a lossy transformer, redrawn in Fig. 2.8. Here the leakage inductance  $((1 - k^2)L_p)$  and magnetizing inductance  $(k^2L_p)$ have been transferred to the primary side. In order to ensure that most of the signal current on the primary  $(I_1)$  is transferred on to the load resistor  $(R_L)$ , we need to ensure that

$$k^2 \omega L_p \gg R_L \tag{2.22}$$

The load resistance  $R_L$  (usually the antenna or the filter input impedance) is typically the same at RF and mm-wave frequencies (i.e., 50 $\Omega$ ). Hence as the operating frequency ( $\omega$ ) increases, the required primary inductance ( $L_p$ ) can be reduced proportionally, while still keeping the impedance ratios the same. This is why transformers have the potential of being very compact at mm-wave frequencies.

Despite the potential for transformers to be very compact at mm-wave frequencies, for transformer-based mm-wave design to be practical, it needs to be demonstrated that the insertion loss of transformers at these frequencies is better than or comparable to distributed transmission lines. Furthermore, a predictable and scalable modeling methodology- good up to mm-wave frequencies- needs to be developed so that transformers can be easily co-designed with the active elements in power amplifier circuits.

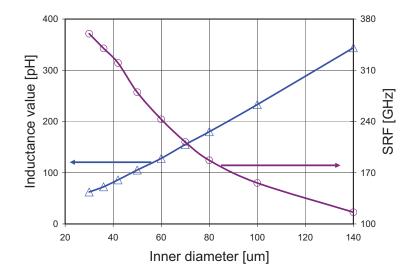

In this work, we use 'overlay' (vertical) configuration for the transformer and utilize the top two metal layers. First, a family of planar octagonal loop inductors was simulated using a full 3-D electromagnetic-field simulator (HFSS) [39]. The effective inductance  $(L_{eff})$ and quality factor  $(Q_{eff})$  of the windings at 60GHz were extracted from the simulated sparameters. Fig. 2.9 shows how the inductance  $(L_{eff})$  and self-resonance frequency (SRF)

Figure 2.8: Equivalent circuit of a 1:1 transformer.

Figure 2.9: Variation of  $L_{eff}$  and SRF with diameter of inductor.

Figure 2.10: Layout of a 1:1 transformer using coupled inductors in a vertical configuration.

Figure 2.11: Variation of insertion loss of transformer at 60GHz as a function of winding diameter.

of an inductor varies as its inner diameter  $(d_{in})$  is increased. Similar plots can be generated for different trace widths as well. From the plot, we see that for reasonable inductor sizes (up to about 350pH), the *SRF* remains above 100GHz.

The loop inductors discussed above were used in an overlay configuration to build vertical 1:1 transformers (Fig. 2.10). Transformers with different diameters and trace widths have been implemented with the top two metal layers. Fig. 2.11 shows the simulated minimum insertion loss of 60GHz transformers, clearly indicating how the size can be optimized. For very small sizes, the impedance of the shunt magnetizing inductance  $(k^2 \cdot \omega \cdot L_p)$  is much smaller than the reflected load impedance and most of the signal current is lost through it. On the other hand, a larger transformer entails more substrate losses and increased series leakage inductance  $((1 - k^2) \cdot \omega \cdot L_p)$  which acts a low pass filter, reducing signal transfer to the secondary size [40]. In the mm-wave domain, where a 90nm CMOS transistor's MSG (maximum stable gain) is only around 8dB, choosing an optimum transformer size is critical to enabling high performance and efficient circuits.

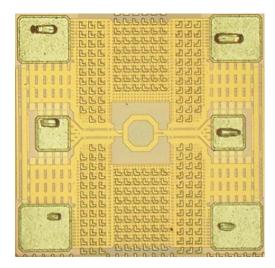

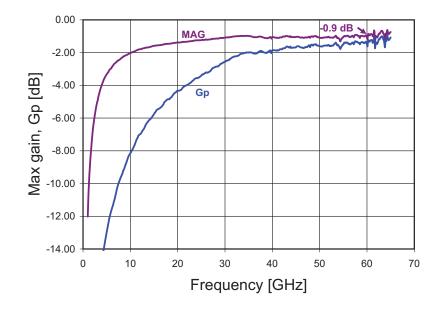

Prototype transformers were fabricated in a 90nm CMOS process [38]. A die photo of the fabricated transformer is shown in Fig. 2.12. The measured and simulated s-parameters show good agreement up to high frequencies. Fig. 2.13 shows the comparison for a 1:1 vertical transformer having a inner diameter of  $42\mu m$  and width of  $8\mu m$ . Fig. 2.14 shows the measured maximum available gain (MAG) and power gain ( $G_p$  for a 50 $\Omega$  load) of the same transformer. From the measurement results, we see that it is possible to design areaefficient transformers at 60 GHz with less than 1 dB of insertion loss. It has been reported in literature that matching networks employing distributed elements like coplanar waveguides

Figure 2.12: Die photo of a transformer with a diameter of  $42\mu m$  and width of  $8\mu m$ .

have insertion loss of the order of 1.2-1.6 dB [3]. Thus we see that transformers can achieve similar performance, with dramatic reduction in silicon area.

Another advantage of transformers which becomes significant at 60GHz is related to the ease of biasing. The center-tap of the transformer winding in a differential circuit is a virtual ground at fundamental frequencies and can be conveniently utilized to provide DC bias. This allows us to eliminate the AC coupling capacitors, which have low quality factor at high frequencies and therefore incur significant loss.

The final advantage of lumped transformers stems from their lower sensitivity to the lossy silicon substrate. Lenz's law states that in an ideal transformer the magnetic flux produced by the current flowing in the primary winding must completely cancel the flux produced by the secondary current. Thus in an ideal transformer with unity coupling coefficient, there is no leakage flux in the area around the transformer. In reality, the coupling coefficient is less than one, and hence complete flux cancelation does not take place. However, the residual leakage flux is still much lower than in an inductor of similar area. This means that less magnetic fields impinge upon the lossy silicon substrate, thereby reducing losses due to effects like eddy current.

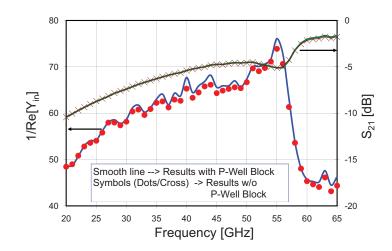

In order to verify this, two transformers were fabricated in 90nm CMOS technology. In one prototype, a p-well block layer was put underneath the transformer to make the substrate less conductive ( $\rho = 10\Omega - cm$ ). In the other prototype, the p-well block layer was removed, thereby making the substrate more conductive and hence more lossy. However, measurements (Fig. 2.15) revealed that there was no difference in the insertion loss ( $S_{21}$ ) and impedance transformation between the two versions, thereby demonstrating the lower sensitivity of transformers to substrate loss.

Figure 2.13: Simulated and measured s-parameters for a vertical transformer.

Figure 2.14: Measured insertion loss for a 1:1 vertical transformer.

Figure 2.15: Dependence of transformer performance on substrate parameters.

#### 2.3.1 Lumped Modeling of mm-wave Transformers

In the previous sub-section, the feasibility of transformers at 60GHz has been established. However, for useful circuit designs, transformers need to be integrated with active elements like transistors. In order to facilitate transformer-based circuit design, a simple model of a transformer, which can accurately predict the performance up to mm-wave frequencies, is needed.

In theory, an ideal 1:n transformer will transform a load resistor of value  $R_L$  to  $R_L/n^2$ , seen from the primary side. However, because of the presence of leakage inductances, parasitic resistors as well as inter-winding coupling capacitor, the impedance transformation at mm-wave frequencies is far from ideal. Fig. 2.16(a) shows the real part of the input impedance at 60GHz for different transformer sizes. As we see from the plot, even though the transformer is always 1:1 and the load resistor  $(R_L)$  and frequency are held fixed, the transformed impedance is a function of the actual size of the transformer. Similarly, Fig. 2.16(b) reveals that the impedance transformation even for a fixed size transformer is frequencydependent. In order to predict the transformer size needed, we need a simple model that can capture these effects.

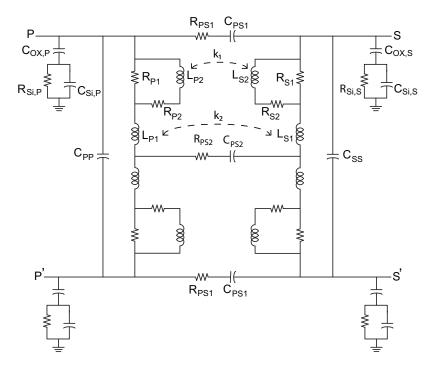

To facilitate transformer optimization, a lumped-element model has been built (Fig. 2.17). It is an extension of a conventional symmetric  $2\pi$  model to mm-wave frequencies [16]. The model parameters are based on a mix of analytical equations and fitting parameters [17]. The dc inductance value of the primary/secondary windings has been calculated by approximating the sides of the spirals by symmetrical current sheets of equivalent current densities. For a given shape, a winding is completely specified by the number of turns (N), the turn width (w), the turn-to-turn spacing (s), and any one of the following: the outer diameter  $(d_{out})$ , the inner diameter  $(d_{in})$ , the average diameter  $(0.5(d_{out} + d_{out}))$ , or the fill ratio, defined as  $\rho = (d_{out} - d_{in})/(d_{out} + d_{in})$ . The expression for winding inductance is given

Figure 2.16: Input admittance of a transformer for a) different winding diameters at 60GHz b) a winding diameter of  $42\mu m$  at different frequencies.

Figure 2.17: Symmetric  $2\pi$  model of transformer

by [41]

$$L_{DC} = \frac{\mu N^2 d_{avg} c_1}{2} (ln(c_2/\rho) + c_3\rho + c_4\rho^2)$$

(2.23)

where  $c_1$ ,  $c_2$ ,  $c_3$  and  $c_4$  are equal to 1.07, 2.29, 0 and 0.19 respectively for an octagonal winding. The dc resistance  $(R_{DC})$  can be calculated from the trace length and metal resistivity. At low frequencies, the primary/secondary winding can be represented as a single inductor with a series resistance to capture the quality factor (Q). However, as we move to higher frequencies, the loss of the winding increases due to the skin and proximity effects. In order to capture this frequency dependence, a ladder network comprising of  $L_{P1}$ ,  $L_{P2}$ ,  $R_{P1}$  and  $R_{P2}$  is used on the primary side and a similar network on the secondary side. In reality, a more distributed approach of modeling the skin and proximity effects using multiple ladder networks yields better results. However, to retain simplicity, we chose one section only since the error incurred by doing that was less than 10%.

From the ladder network, the dc inductance and resistance values of the primary winding can be calculated as [16]

$$L_{DC} = L_{P1} + \left(\frac{R_{P1}}{R_{P1} + R_{P2}}\right)^2 \cdot L_{P2}$$

(2.24)

$$R_{DC} = \frac{R_{P1}R_{P2}}{R_{P1} + R_{P2}} \tag{2.25}$$

Using Eq. 2.23-2.25, we fit the component values of the elements of the ladder network.

The substrate network consists of oxide capacitance  $(C_{OX})$  and substrate capacitance and resistance  $(C_{SUB}, R_{SUB})$  whose values have been calculated using process parameters and geometry of the windings. However, it is important to note that since we are utilizing a vertical transformer built out of the top two metal layers, the top winding has a different oxide capacitance than the bottom one, and in fact is shielded by the bottom winding. To account for this, asymmetric substrate networks have been used for the primary and secondary windings. Finally, to correctly capture the self-resonance frequency of the transformer, the winding self-capacitance  $(C_{PP}$  and  $C_{SS})$  and inter-winding capacitance  $(C_{PS})$ have been included in the model and have been calculated using parallel plate capacitance equations and adding fringing capacitance to it.

Fig. 2.18 shows a comparison of the Z and S-parameters obtained from the model (for a  $42\mu m$  transformer) to the 3D electromagnetic simulation results using HFSS. From the graphs, we see that there is good agreement between the results even up to 80GHz. As a metric of the performance of the transformer, we show a comparison between simulated and modeled  $G_p$  (power gain) of the transformer (Fig. 2.18(d)). A good match between the two shows that the model used here is indeed physical.

Figure 2.18: Comparison between simulated and model results a)  $Z_{22}$  b)  $Z_{21}$  c)  $S_{11}/S_{21}$  and d)  $G_p$ .

#### 2.3.2 Distributed Modeling of Transformers

The previous section demonstrated that a lumped element approximation of an on-chip transformer is valid even at the mm-wave frequencies. However, the model developed above involves a large number of parameters, some of which can be calculated accurately from geometry, but many are fitting parameters to match the modeled results to measurements. Consequently, it is very difficult to make such a model truly scalable with transformer size (winding diameter) and hence difficult to use efficiently during the design phase. We have proposed therefore a simplified distributed model of a transformer [42], which is length-scalable and involves far fewer parameters. However, as will be demonstrated next, it has high accuracy in predicting the input impedance and insertion loss up to mm-wave frequencies.

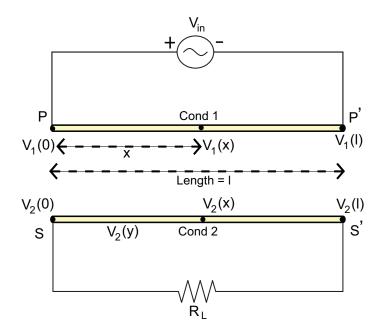

The fundamental observation that leads to this model is that because of the presence of significant inter-winding capacitance, the energy transfer from the primary to the secondary winding is not only through magnetic field coupling (inductive), but also through electric field (capacitive). Hence, as shown in Fig. 2.19, the transformer can be viewed as a broadside-coupled differential transmission-line (t-line). The parameters needed to charac-

Figure 2.19: Distributed modeling of a transformer as coupled transmission-lines.

terize a transmission line are its characteristic impedance  $(Z_0)$  and its complex propagation constant  $\gamma$  ( $\gamma = \alpha + jk$ ), where  $\alpha$  is the attenuation constant and k is the propagation factor. Thus, if we are able to represent a transformer as a transmission-line, we require far fewer parameters to capture its behavior accurately [43].

Fig. 2.20 shows the simulated odd-mode characteristic impedance  $(Z_0)$  and attenuation factor  $(\alpha)$  over frequency for a vertical transformer with a trace width of  $5\mu$ m and winding diameter of  $30\mu$ m. The flatness in  $Z_0$  over the mm-wave frequency range shows that it is indeed possible to model the transformer as a transmission line.

However, in representing a transformer as a transmission line, proper attention needs to be paid to how it is excited and the resulting modes of operation [42]. Referring to Fig. 2.19, if the structure would have been used as a normal transmission line in a differential circuit, ports P and S would have been excited differentially and ports P' and S' would have been terminated in the load resistor  $R_L$ . However, in a transformer, we represent the primary winding as one conductor of the t-line and the secondary winding underneath it is the second conductor of the coupled-pair t-line. Hence, when the primary winding is excited differentially, we are applying that excitation across ports P and P', while the secondary winding (ports S and S') is terminated in  $R_L$ . This means that even though the transformer is excited differentially, with respect to the transmission line (ports P and S) both odd and even modes of propagation are excited. This is even more true since in a power amplifier, the output transformer is also utilized as a balun and hence one of the output ports is grounded. Thus, in order to capture the complete behavior, we need to take into account both the odd

Figure 2.20: Characteristic impedance  $(Z_0)$  and loss factor  $(\alpha)$  of a  $30\mu$ m diameter transformer, excited as a transmission line.

(differential) mode and even (common) mode parameters  $(Z_0, \alpha \text{ and } k)$  of the transmission line.

A simplified set of equations that govern this modeling are shown below [44]. Here,  $V_{d+}$  and  $V_{d-}$  represent the odd-mode forward and reverse travelling waves, while  $V_{c+}$  and  $V_{c-}$  represent the same for the even mode.  $Z_d$  and  $Z_c$  are the odd-mode and even-mode characteristic impedances respectively. While  $Z_d$  is primarily dependent on the spacing between the two conductors (the dielectric thickness between the top two metal layers in our case of vertical transformer),  $Z_c$  is mostly determined by the adjacent ground structures. Given a winding geometry (octagonal shape in our design), the length of the line (l in Fig. 2.19) is determined by the winding diameter. For simplicity, the lines have been assumed as lossless ( $\alpha = 0$ ) in these equations. The real loss has been incorporated in the final model and its frequency dependence has been captured by a simple square-root function. The parameters required for the coupled line model have been extracted from HFSS simulation.

$$V_1(x) = V_{d+}e^{-jkx} + V_{d-}e^{jkx} + V_{c+}e^{-jkx} + V_{c-}e^{jkx}$$

(2.26)

$$V_2(x) = -V_{d+}e^{-jkx} - V_{d-}e^{jkx} + V_{c+}e^{-jkx} + V_{c-}e^{jkx}$$

(2.27)

$$I_1(x) = V_{d+}e^{-jkx}/Z_d + V_{d-}e^{jkx}/(-Z_d) + V_{c+}e^{-jkx}/Z_c + V_{c-}e^{jkx}/(-Z_c)$$

(2.28)

$$I_2(x) = -V_{d+}e^{-jkx}/Z_d - V_{d-}e^{jkx}/(-Z_d) + V_{c+}e^{-jkx}/Z_c + V_{c-}e^{jkx}/(-Z_c)$$

(2.29)

Imposing current continuity and voltage boundary conditions, we can solve for the input

Figure 2.21: Comparison between measured and t-line based model results for a) input admittance  $(Y_{in})$  and b) power gain  $(G_p)$ .

impedance looking into the primary winding as

$$Z_{in} = (V_1(0) - V_1(l))/I_1(0)$$

(2.30)

Using Eq. (2.26) - (2.29) in Eq. 2.30, we get

$$Z_{in} = \left\{ \frac{\sin\left(\frac{kl}{2}\right) \left(4Z_c Z_d \tan\left(\frac{kl}{2}\right) + jR_L(Z_c + Z_d)\right)}{R_L \cos\left(\frac{kl}{2}\right) - j(Z_c + Z_d) \sin\left(\frac{kl}{2}\right)} \right\}$$

(2.31)

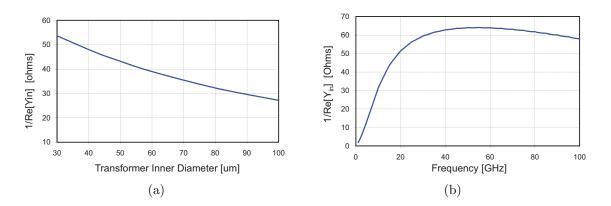

The above equations (with the odd-mode and even-mode losses) have been implemented using "CLINP" (coupled lossy transmission line) in ADS and the s-parameters predicted by the model match both measurements and full 3-D simulations over a very wide frequency range. Fig. 2.21(a) shows a comparison between the measured and modeled real and imaginary parts of input admittance of the vertical transformer with  $30\mu$ m diameter, while Fig. 2.21(b) shows that the modeled insertion loss matches measurements closely. The measurements were carried out up to 65 GHz (limited by the available VNA).

A significant advantage of this model is its scalability property. If the trace width of the windings is kept fixed, the characteristic impedance  $(Z_o)$ , loss coefficient  $(\alpha)$  and propagation constant (k) all remain constant. Hence, the only parameter that needs to be altered in the model for a different size transformer is the length of the transmission line, which is directly a function of the winding diameter. Thus, we see that compared to the lumped model, this holds significant advantage, since the performance of a broad family of transformers with the same trace width can be estimated easily without any additional parameter fitting. For transformers with different trace widths, the  $Z_o$  and  $\alpha$  change, but can be calculated analytically based on the transmission line configuration [45]. Thus, even in these cases,

the model proves to be beneficial, as only two parameters ( $Z_o$  and  $\alpha$ ) need to be made width-dependent, compared to more than 20 parameters in a lumped model.

The scalability of the model has been verified by increasing the winding diameter from  $30\mu$ m (transformer in Fig. 2.21) to  $100\mu$ m. As expected, the insertion loss and the sparameters were well predicted by the model for the new transformer and the only parameter that had to be modified in the model was the t-line length (l). The distributed transformer model proves to be a valuable tool in designing optimized mm-wave circuits, as will be demonstrated in Chapter 3. It should be pointed out that the distributed modeling methodology has been applied to 1:1 transformers only. For higher turns ratio, there exists coupling between multiple primary (or secondary) windings. The extension of such a modeling approach to higher turns ratio transformers could be an interesting extension of this work.

## 2.4 Transformers and Transformer-Based Power Combiners at RF Frequencies

The design, layout and modeling of transformers developed in the previous section are also valid at RF frequencies. However, at 2.4GHz, the inductance required for proper operation is larger than mm-wave frequencies, which makes the transformer footprint at these frequencies larger. As a consequence, the winding parasitic resistances are higher and in high-power applications, this translates into increased insertion loss. Thus, additional techniques are required to make RF transformers efficient. Furthermore, at 60GHz, the required output power in PA circuits is in the low to moderate range (around 10 dBm). This means that huge impedance transformation ratios are not required and 1:1 transformers often suffice. However in the lower GHz wireless applications like WLAN, the required power levels are much higher (> 20 dBm). This necessitates higher impedance transformation, like 2:1 or 3:1 transformers. Minimizing the insertion loss in such structures is fairly challenging. In this work, two techniques- the parallel-primary 2:1 transformer and transformer-based power combiners- have been developed that can achieve higher impedance transformation ratio with low insertion loss. Transformer based power combiners are particularly attractive since they can realize higher turns ratio by using only 1:1 transformers. The distributed modeling technique can thus be employed to analyze power combiners as well.

#### 2.4.1 A 2.4GHz Parallel-Primary Transformer with Interwound Secondary

Fig. 2.22 shows a conventional layout of a 2:1 transformer, where the secondary winding is wound symmetrically around the primary winding. Such a layout has two distinct shortcomings. First, the width of the primary winding needs to be very large to have low series

Figure 2.22: Layout of a conventional symmetric 2:1 transformer.

Figure 2.23: Current distribution in two parallel conductors carrying current in opposite directions.

Figure 2.24: Modified layout of a 2:1 transformer with parallel primary.

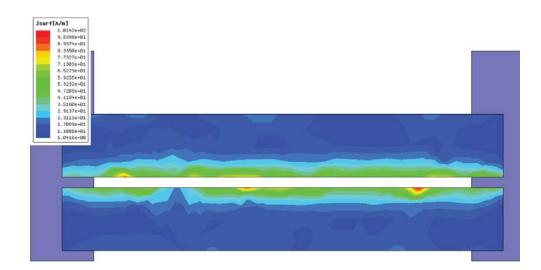

resistance as well as to satisfy electromigration requirements in high-current applications like PA design. In fine-line CMOS processes, the maximum allowed width of the metal trace is limited to  $10 - 12\mu m$ , which is often lower than the optimal value based on loss considerations. An increase in trace width would require either a violation of the standard design rules or would require metal slotting, both of which are undesirable. The second disadvantage of the conventional layout stems from the proximity effect. At RF frequencies, when two parallel conductors carry current in opposite direction, the currents tend to get concentrated along the adjacent edges. In order to verify this, a full-wave 3D electromagnetic simulation was carried out in HFSS with two parallel conductors which were excited to carry currents in opposite directions. Fig. 2.23 shows the simulated current density is indeed higher along the adjacent edges of the parallel conductors. Since the current is not uniformly distributed along the surface of the conductor, it increases the effective AC resistance, which leads to higher insertion loss.

The above shortcomings have been overcome in our proposed layout of parallel-primary transformer, as shown in Fig. 2.24 [46]. In this 1:2 transformer design, we have split up the

Figure 2.25: Simulated insertion loss of parallel primary transformer.

single primary turn into three parallel primary windings. Thus, the effective DC resistance of the primary winding is cut by a factor of three, compared to the resistance of the maximum width metal allowed by design rules. However, instead of just placing the three primary windings side by side, they are intertwined symmetrically around the two series-connected secondary windings, as shown in Fig. 2.24 [37] [47]. Such an arrangement reduces the loss due to proximity effect. Since each secondary winding now sees a primary winding on either side of it, the current in the winding is better distributed, cutting down the AC resistance. In the layout of this transformer, no ultra thick metal (UTM) or special RF options have been utilized. Fig. 2.25 shows the simulated insertion loss of the transformer around 2.4GHz. The transformer response is fairly broadband, with insertion loss  $\leq 1.6dB$  all the way from 1.9-4GHz. The design of a digitally modulated power amplifier, employing this 2:1 transformer will be described in Chapter 5.

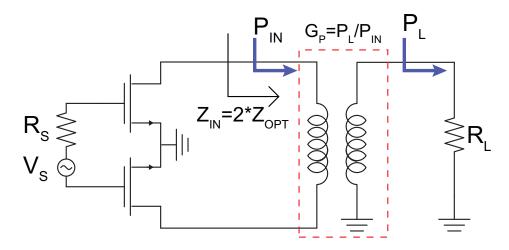

#### 2.4.2 Transformer Based Power Combiner Design